〇 概要

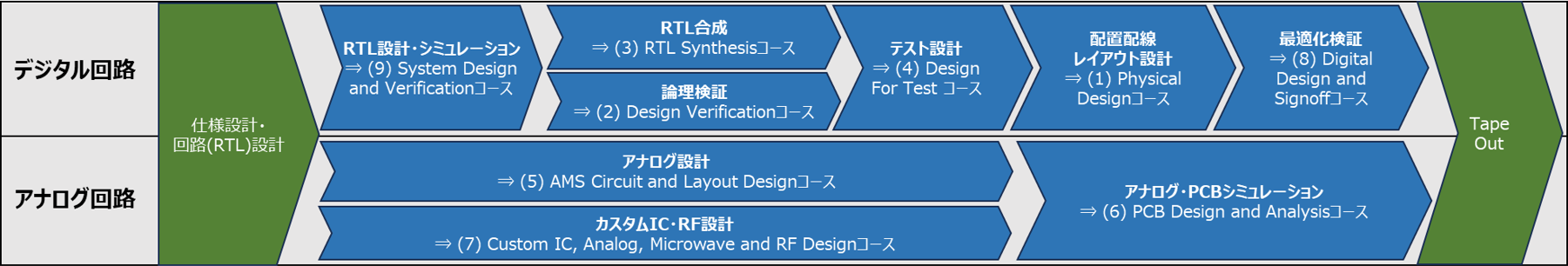

初級コースでは、以下のSoC設計フローの各工程に合わせた9つのコースによって、世界の先端EDA ツールを使いこなすことのできるスペシャリストを育成します。

9つのコースは各々独立した内容となっているため、希望するコースだけを選んで受講することが可能です。

➢ 目指す設計人材像

先端EDAツールを使いこなし、適正な品質で効率よく設計・検証を行うことができるスペシャリスト

コース修了後、半導体産業で上記のような人材として10年以上活躍する意欲のある方を募集します。

〇 募集要項

| 受講対象 | 本コースの受講者は以下を対象としています。 ・日本国籍を有し、かつ日本に居住している方 ・大学工学部電気系等卒業程度の学力、回路システムに関する知識を有している方 ・Linux、Tcl/Tk、Perl、およびPythonなどの基本的なプログラミングに習熟している方 ・事前テストに合格していること。(事前テストについてはこちらでご確認ください) |

| 修了要件 | 各講座で実施する修了テストの結果や、講義出席状況などを鑑みて修了可否を判断します。修了が認められた場合は、コースに応じてSynopsysの認証バッジ(Certification)、またはCadenceの認定書をお渡しします。 |

| 費用負担 | 本プログラム中、すべてのコースにおいて受講料は発生しません。ただし、講座や実習場所までの旅費交通費、食事代等は、受講生の自己手配・自己負担となります。 |

| 受講環境 | オンライン受講では、PCのブラウザが必要です。また、音声が聞こえるよう、ヘッドフォン等をご用意ください。 対面受講では、講座受講施設に用意されたPCをご使用いただきます。 |

| 所属先への確認 | 本コースには対面講座や、長時間のオンライン講座があります。一時的に職場を離席して受講いただくことになるため、必ず所属先の上長や職場(または学校)の責任者からの了承を得たうえで申請をしてください。 |

➢ コース一覧

各コースの詳細内容は、表のリンク先よりご確認いただけます。

※2026年度も全9コース開講します。日程は決定次第順次公開します。

| コース | 受講申込期間 | 開講期間 | 学習目安時間 (オンライン) | 受講方法 | 定員 |

|---|---|---|---|---|---|

| (1) Physical Designコース | 締め切りました | 2月1日~4月30日 | 80時間 | オンライン(オンデマンド形式) | 25名 |

| 2026年度開講予定 | 25名 | ||||

| (2) Design Verificationコース | 締め切りました | 2月1日~4月30日 | 40時間 | オンライン(オンデマンド形式) | 25名 |

| 2026年度開講予定 | 25名 | ||||

| (3) RTL Synthesisコース | 締め切りました | 2月1日~4月30日 | 40時間 | オンライン(オンデマンド形式) | 25名 |

| 2026年度開講予定 | 25名 | ||||

| (4) Design For Testコース | 締め切りました | 2月1日~4月30日 | 30時間 | オンライン(オンデマンド形式) | 25名 |

| 2026年度開講予定 | 25名 | ||||

| (5) Analog & Mixed Signal (AMS) Circuit and Layout Designコース | 締め切りました | 2月1日~4月30日 | 45時間 | オンライン(オンデマンド形式) | 25名 |

| 締め切りました | 3月1日~5月31日 | ||||

| 2026年度開講予定 | 25名 | ||||

| (6) PCB Design and Analysisコース | 締め切りました | 1月14日~2月12日 | 80時間 | オンライン(オンデマンド形式) | 14名 |

| 2026年度開講予定 | 14名 | ||||

| (7) Custom IC, Analog, Microwave and RF Designコース | 締め切りました | 2月1日~3月31日 | 115時間 | オンライン(オンデマンド形式) | 14名 |

| 2026年度開講予定 | 14名 | ||||

| (8) Digital Design and Signoffコース | 締め切りました | 2月26日~3月25日 | 75時間 | オンライン(リモート形式) | 14名 |

| 2026年度開講予定 | 調整中 | 14名 | |||

| (9) System Design and Verificationコース | 締め切りました | 2月2日〜2月25日 | 75時間 | オンライン(リモート形式) | 14名 |

| 締め切りました | 3月1日~3月24日 | オンライン(オンデマンド形式) | 14名 | ||

| 2026年度開講予定 | 調整中 | 14名 | |||

➢ 申込手順

応募から受講開始までの流れは、下の図のようになります。次項より申込手順を詳述します。

Step0.

受講要件の確認

本プログラムは日本の半導体産業において即戦力となるような設計者、アーキテクトを育成し、中長期にわたって日本の産業に資する人材を育成することを目的としています。この趣旨に賛同し長く半導体産業で活躍したいという意欲のある方を、募集します。

本プログラムは半導体設計技術者の育成を目的とし、初級・中級(日本国内で実施)から上級(日本国内・米国で実施)レベルのスキルまで一貫して学べるように構成されています。そのため本プログラムは以下の日本および米国の法令等を遵守する等、 技術流出防止にも配慮します。またカリキュラムの提供に協力いただいている企業等の競争上の地位その他正当な利益を害する恐れの無いように配慮します。

- 外国為替及び外国貿易法(外為法)

- 米国輸出管理規則(EAR)

受講には、以下の要件をいずれも満たしていることも必要です。

- 日本国籍を有すること

- 日本に居住していること

Step1.

ユーザ登録

受講申込には、ユーザ登録が必要です。登録フォームに以下の情報を入力し、登録申請を行ってください。

- 申請者本人の情報

- 氏名

- メールアドレス

- 国籍

- 居住国

- 年代

- 電話番号

- 勤務先、所属先の情報

- 名称

- 部署・部門/研究室

- 所在地

- URL

申請後5営業日以内に、ADIP運営事務局(以下、「事務局」)よりマイページのご案内メールを送信します。

マイページから、各コースへの受講申込を行ってください。

※登録内容によっては、申請が受理されない場合もあります。

※info@adip.jp が受信可能となるようご自身のメーラーの設定をお願いいたします。

Step2~3.

事前テストの申込

~事前テスト受験

Step4.

受講申込

マイページから、希望するコースへの受講申込を行ってください。申込には、次の情報が必要です。

- 受講を希望する講座

- 受講目的

- 所属機関からの受講承認を得ていることの確認

申込締切後一両日中に、事務局より受講案内をお送りします。

※定員に達し次第、申込を締め切ります。応募数超過の場合、申込を受理できない可能性がありますのでご了承ください。

講座修了後は、マイページに修了したコースの履歴が表示されます。

〇 注意事項

- 講座はすべて日本語で行われます。

- ユーザ登録申請をする際のメールアドレスは、所属組織が支給する、個人が特定できるメールアドレスに限ります。グループメールや複数の方で共有するメールアドレスでの申請はできません。また、MicrosoftやGoogle等がそれらの従業員以外の一般会員に提供したメールアドレス等での申請もできません。

- マイページの案内は、事務局の審査により本プログラムの受講が認められた方へお送りします。この際の個人情報の取り扱いについては、別途定めるプライバシーポリシーをご参照ください。なお、事務局が受講を認めないと判断した場合でも、不許可の理由は開示いたしませんのでご了承ください。

〇 応募情報の取り扱いについて

応募に際し申請フォーム等に記載された個人情報のうち、受講可否の審査や通知、受講案内などに必要な情報は、事務局内で共有されます。

またアンケートや特定の個人を識別しない状態に加工した統計資料等に利用することがあります。応募者の個人情報は上記目的以外で利用することはありません(法令等により提供を求められた場合を除く)。詳細は、別途定めるプライバシーポリシーをご参照ください。