内容やスケジュールは変更になる可能性があります。

コース概要

他者が設計したIPのRTLデザインをSoCに組み込むまでのフローを学習する。論理合成、タイミング設計、テスト設計等を行い、バックエンド設計者へ引き渡せるよう、ネットリスト等の設計データを作成・整備する。同時に、RTL設計者にデザインの問題点をフィードバックできるスキルを身に着ける。

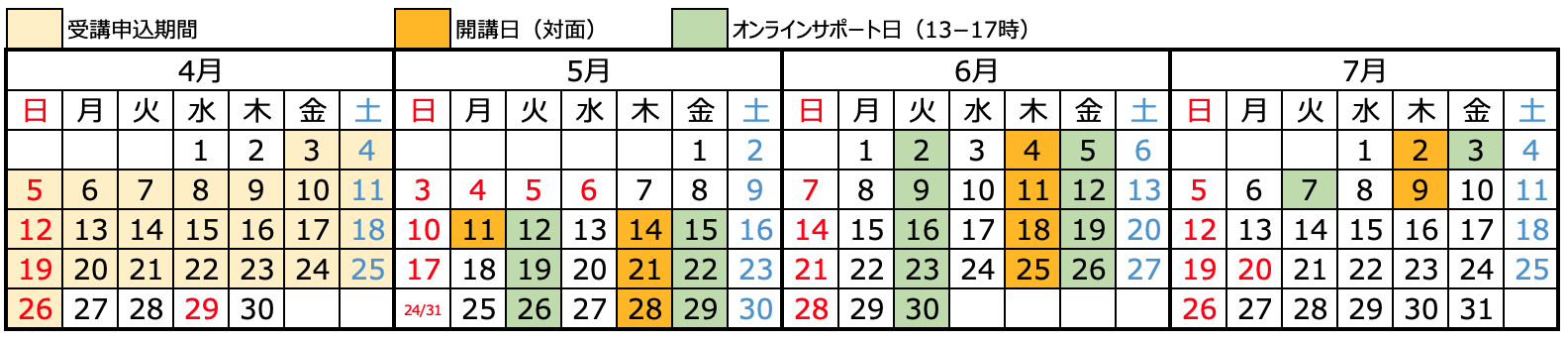

開講スケジュール

2026年5月11日~7月9日 全10回(13時~17時)

受講申込期間:4月3日〜4月26日

原則として、毎週木曜日13:00に東京大学の講義室へ出席していただきます。

※出席が難しい場合はビデオ会議によるオンライン参加も可能です。

オンラインサポート日にはオンライン受講システムを通じて、リモートでの質問や講師への相談にも対応します。

本コースの受講には、事前テストの合格が必要です(既に合格している場合、再受験は不要)。

講義テーマ

回路設計

SoC仕様に基づき、設計データの各ディレクトリの構造を理解し、IPをSoCとしてインテグレートする。組上げたSoCの論理検証を、論理シミュレータを用いて行う。

さらに目標動作周波数などに基づきタイミング制約、合成制約の設計を行う。設計したデータの静的検証を行い後の設計工程で問題が生じないように設計品質を確保する。大規模な設計データを用いることで大量に発生するエラー、ワーニングレポートをツールの機能も使いながら的確かつ効率的に処理する能力を養う。

論理合成

設計したロジックライブラリ等の合成環境と設計したRTL、タイミング制約、合成制約、EDAツールを用いて論理合成を行い、ツールのレポートをもとに合成結果が要件を満たしているか検証を行う。さらに合成結果のゲートネットリストと元のRTLの等価検証を実施する。大規模な設計データを用いることで大量に発生するエラー、ワーニングレポートをツールの機能も使いながら的確かつ効率的に処理する能力を養う。

テスト設計

論理回路へのスキャンテスト回路の挿入とメモリをテストするメモリーBISTの挿入を行ったのち、挿入前後の回路の等価検証を実施する。また、スキャンテスト回路の挿入による新たなタイミング違反がないかタイミング検証も実施する。最後にゲートレベルの論理シミュレーションを行いテストが正しく行えることを検証する。論理検証を行う際には1チップシミュレーション環境を利用する。

ゴール

- 論理設計者から入手したRTLを基にタイミング要件を満たす条件を設定し、論理合成とテスト回路の挿入が行えるようになる。

- バックエンド用に提供するネットリストとタイミング制約を作成できるようになる。

- 発生するエラー/疑似エラーへの対処方法や、フォーマル検証の実施するスキルを習得する。