内容やスケジュールは変更になる可能性があります。

コース概要

フロントエンド設計者から提供される設計データを用いたチップレイアウトから、生成されたレイアウトデータ検証までの手法を習得する。この工程中に発生する問題点やその解決方法を学ぶほか、EDAツールから出力されるレポートを解析し、フロントエンド設計者に情報をフィードバックできるスキルも身に着ける。

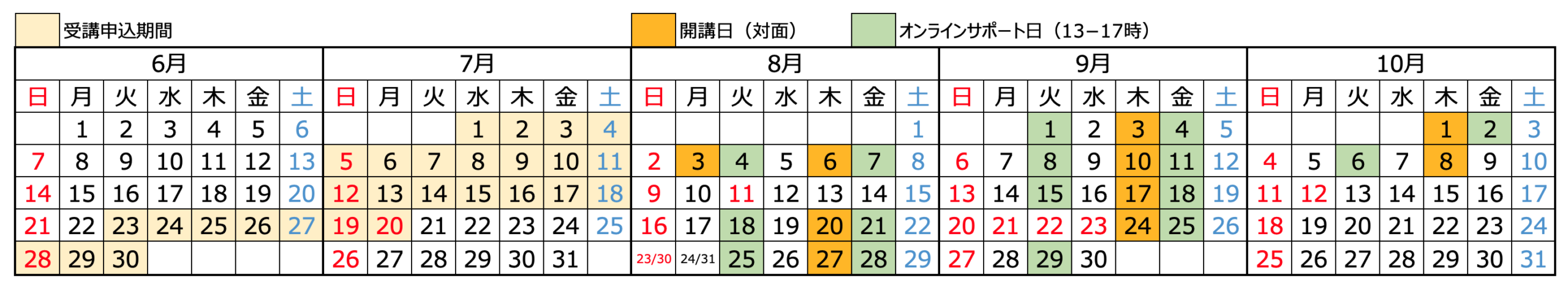

開講スケジュール

2026年8月3日〜10月8日 全10回(13時~17時)

受講申込期間:2026年6月23日〜7月20日

原則として、毎週木曜日13:00に東京大学の講義室へ出席していただきます。

オンラインサポート日にはオンライン受講システムを通じて、リモートでの質問や講師への相談にも対応します。

本コースの受講には、事前テストの合格が必要です(既に合格している場合、再受験は不要)。

講義テーマ

1.実装設計

フロントエンドから提供されたRTL等の設計データの受入検査として、RTL設計ガイドラインにのっとっている設計データであるかをツールのCFチェック項目に従い実行する。結果のレポートファイルの確認を行い、その後はPlace & Routeツールを用いてフロアプラン、Placement、Clock Tree Synthe sis、Routing、Post Route Optimizationを行う。必要であればフロントエンド設計者へのフィードバックを行う。

同様に、DFレベル、CFレベルの設計データについても受入検査とレポートファイルの確認を行い、Place & Routeツールを用いてフロアプラン、Placement、Clock Tree Synthe sis、Routing、Post Route Optimizationを行う。

2.実装検証

タイミングチェック(STA)

CFレベル論理でレイアウトが完了したデータに対し、設定された条件でのSTAを実施し、レポータ解析を行う。必要な場合はECOを実施し、等価検証を行う。レイアウトでのECOで対策が十分できない場合には実装設計のフロアプランの工程からやり直す。

IR Drop検証、エレクトロマイグレーション チェック

CFレベル論理でレイアウトが完了したデータに対し、消費電力シミュレーション波形を利用したIR Drop検証、エレクトロマイグレーション チェック、レポータ解析を行う。必要な場合はECOを実施し、等価検証を行う。レイアウトでのECOで対策が十分できない場合には実装設計のフロアプランの工程からやり直す。

DRC/LVS/PERC

CFレベル論理でレイアウトが完了したデータに対し、プロセルルール、デバイスルールを用いたDRC/LVS/PERCを行い、レポータ解析を行う。

ゴール

- フロントエンドから入手したネットリストを利用し、タイミング制約を満たしたSoCのレイアウトに実装できる。

- 寄生容量抽出後、消費電力のIR Drop検証、エレクトロマイグレーションチェック、DRC/LVS/PERCチェックを行える。

- 上記チェック結果が守れない場合の対処法を習得する。