目次

(1) Physical Designコース

(2) Design Verificationコース

(3) RTL Synthesisコース

(4) Design For Testコース

(5) Analog & Mixed Signal (AMS) Circuit and Layout Designコース

(6) PCB Design and Analysisコース

(7) Custom IC, Analog, Microwave and RF Designコース

(8) Digital Design and Signoffコース

(9) System Design and Verificationコース

日程や内容は変更の可能性があります。

(1) Physical Designコース

コース概要

このコースでは、フィジカル・デザインに必要なすべての知識を習得し、最新EDA ベンダのツールを実際に体験することができます。

最先端の商用EDAツールを使って物理設計(バックエンド設計)を学習します。EDAで利用されるフィジカルライブラリの作成やRTLからGDS IIへのフロー、そして、Fusion CompilerやIC Compiler IIを使ったデザイン作成や合成、クロックツリー生成や配線の最適化、そして、タイミング解析、寄生抽出の手法を習得することができます。

内容

① フィジカル・デザインⅠ

このフィジカル・デザイン入門トレーニングでは、フィジカル・ライブラリの作成とその特性データについて説明し、最後にフィジカル・デザインRTL から GDS II までのフロー(抽象化、タイミング、シグナル・インテグリティ、ローパワー、UPF、DFT、ライブラリ準備、ライブラリ作成、制約設定)を紹介します。

② フィジカル・デザインⅡ

フィジカル・デザイン・インプリメンテーションの包括的な機能について詳しく説明します。最新EDA ベンダのFusion Compiler を実際にご覧ください。このデモベースのコースでは、フロアプランニング、配置、クロックツリー合成からECO フローによる配線最適化までが含まれ、最後にインプリメンテーション・フローにおける新たなノードの影響とソリューションが紹介されます。

③ ジャンプスタート

Fusion Compiler インプリメンテーション手法、PrimeTime を使用したスタティックタイミング解析サインオフ、StarRC を使用した寄生抽出のジャンプスタートトレーニングを行います。

④ Fusion Compiler

Fusion Compiler を使用して完全なフィジカル合成を実行する方法を学びます。モジュールには、GUI の使用方法と豊富な GUI 演習、デザインライブラリの作成、スタンダードセルとIP ライブラリの参照、RTL の読み込みと “ダーティ “または不完全なRTL の処理、オブジェクト、ブロック、アプリケーションオプションの理解、FusionCompiler フローの 7 つの最適化ステージの詳細、フィジカル合成に必要な絶対最小限のセットアップが含まれます。加えて、Fusion Compiler 以降の統一フローを継続します。詳細なモジュールでは、クロックツリー合成、配線、配線後の最適化、ブロックレベル設計のサインオフ操作などをカバーします。ここでは、詳細なスクリプトを使用した広範な実習が含まれます。

使用ツール

- Synopsys Fusion Compiler

- Synopsys PrimeTime

- Synopsys StarRC など

主な対象者

- デザインチームに新規採用された社員

- VLSI設計を始めるキャリア・スターター

- 学士課程、修士課程修了見込みの学生

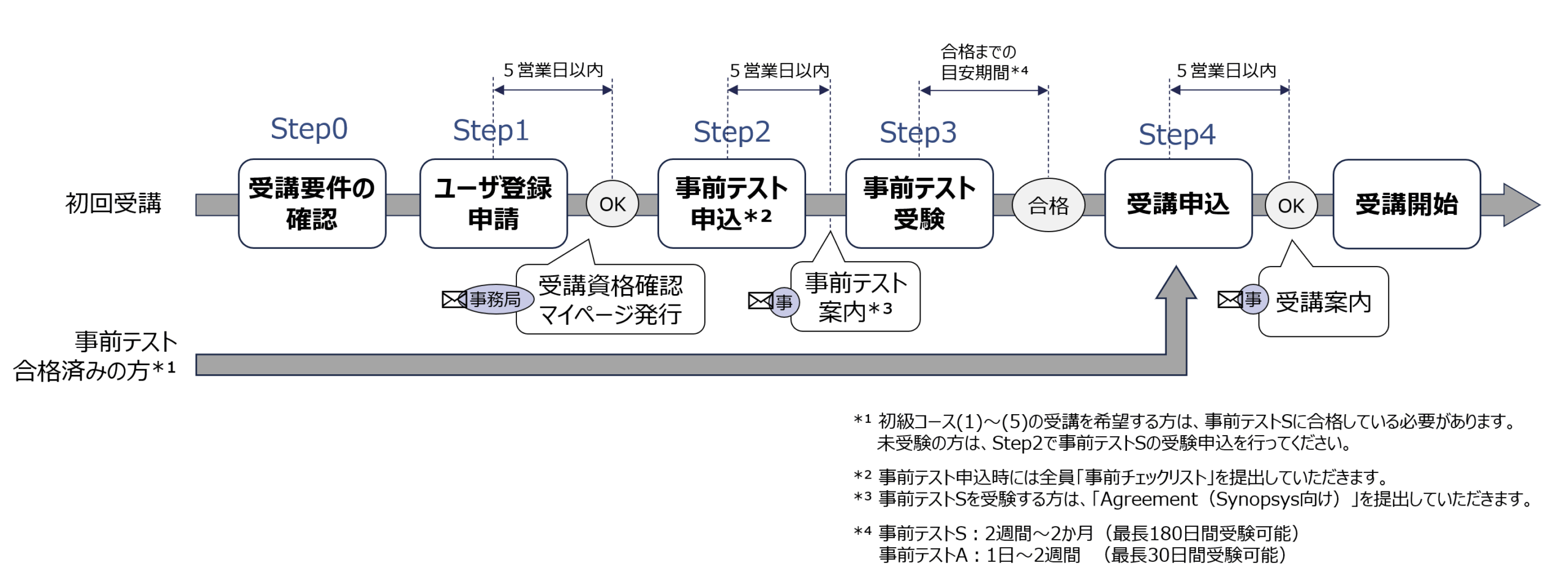

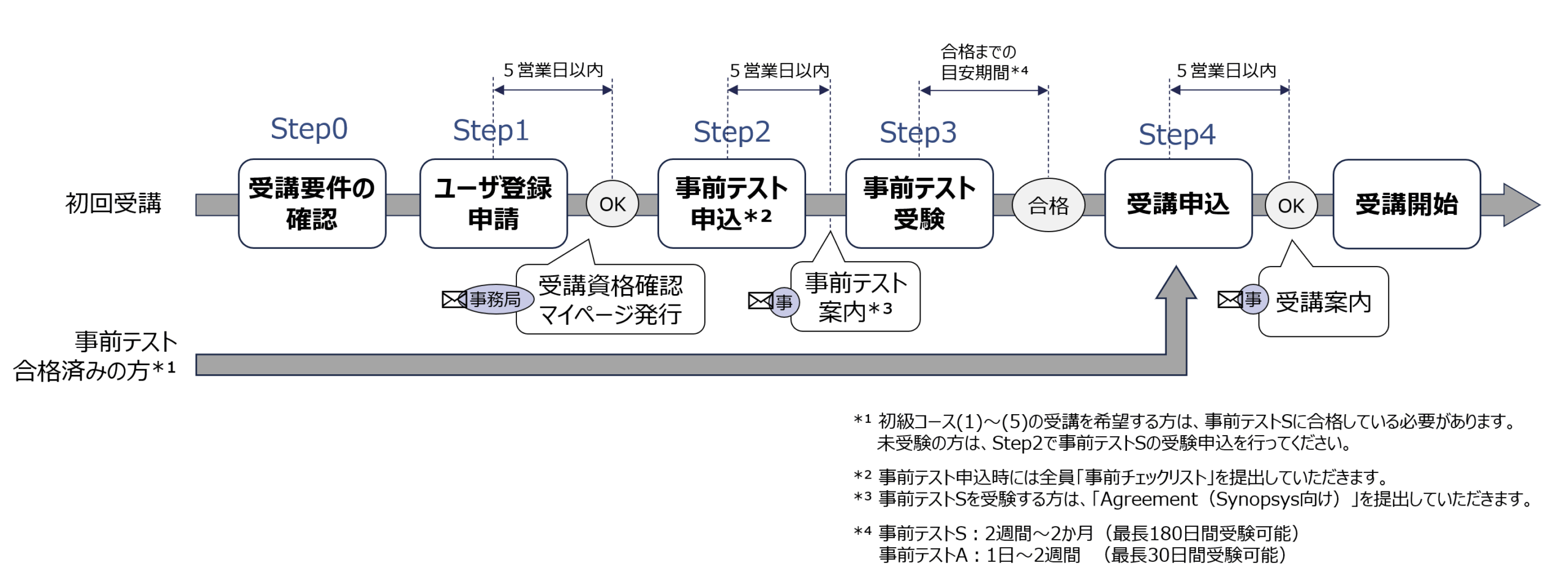

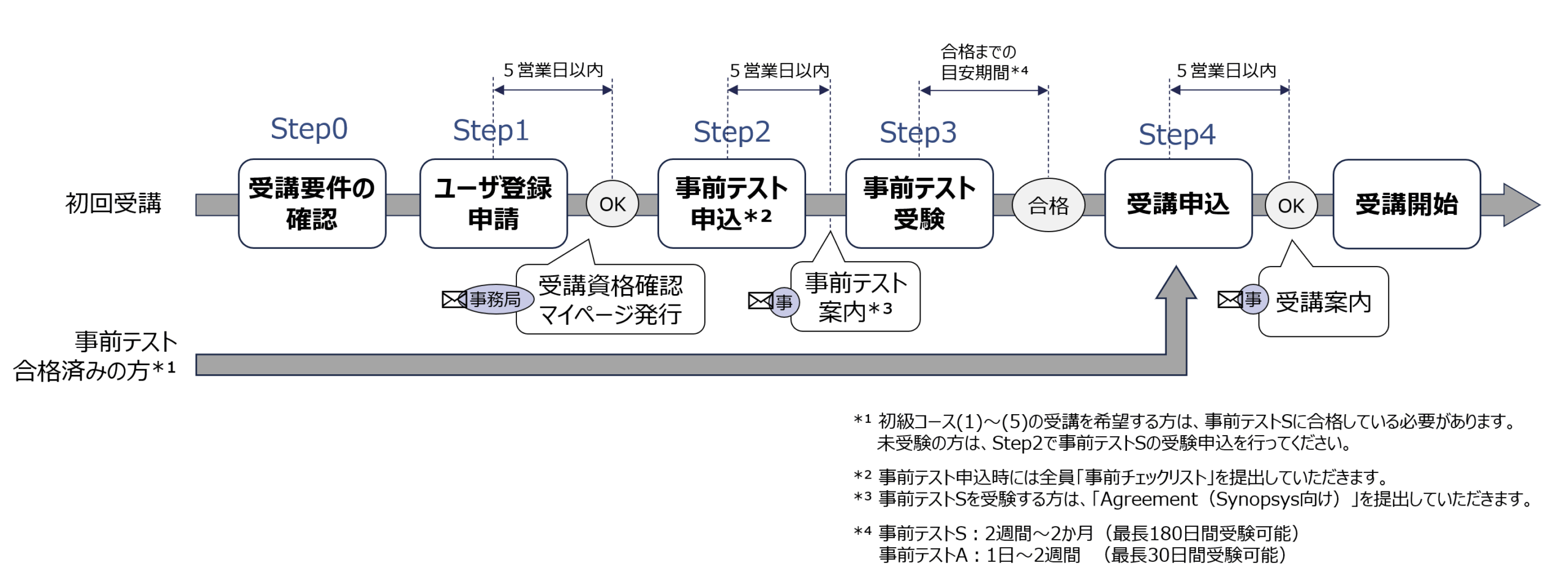

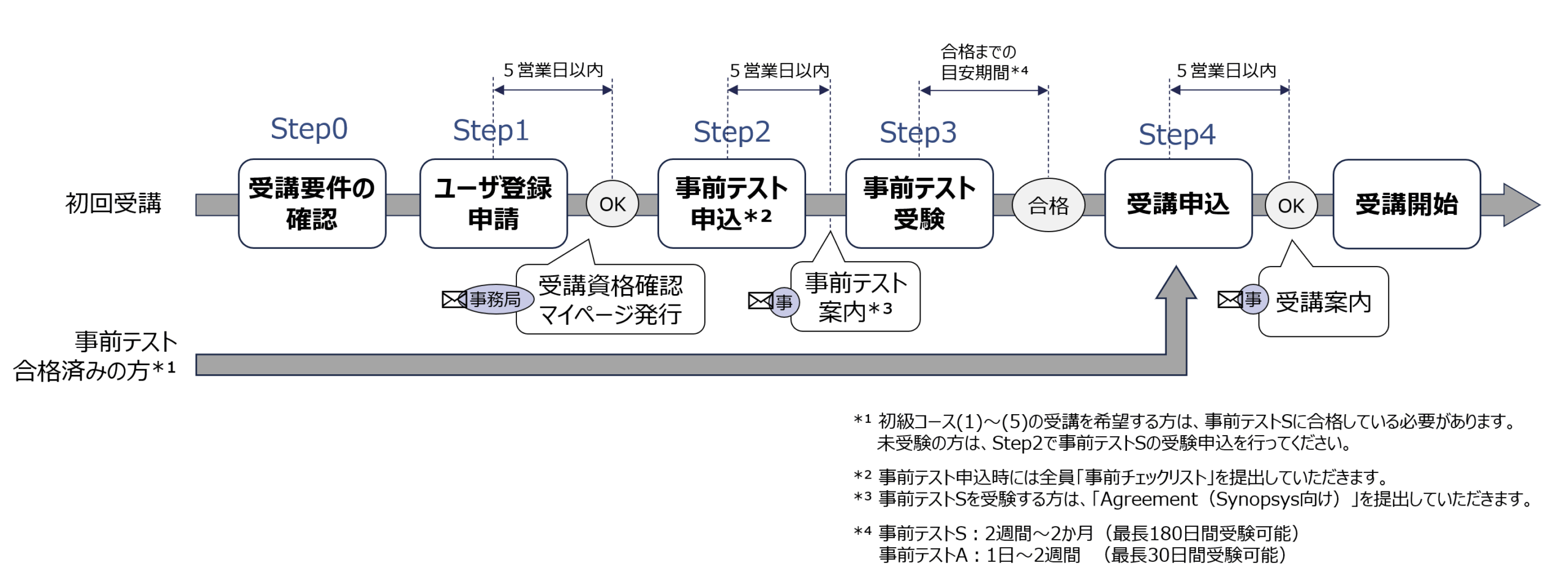

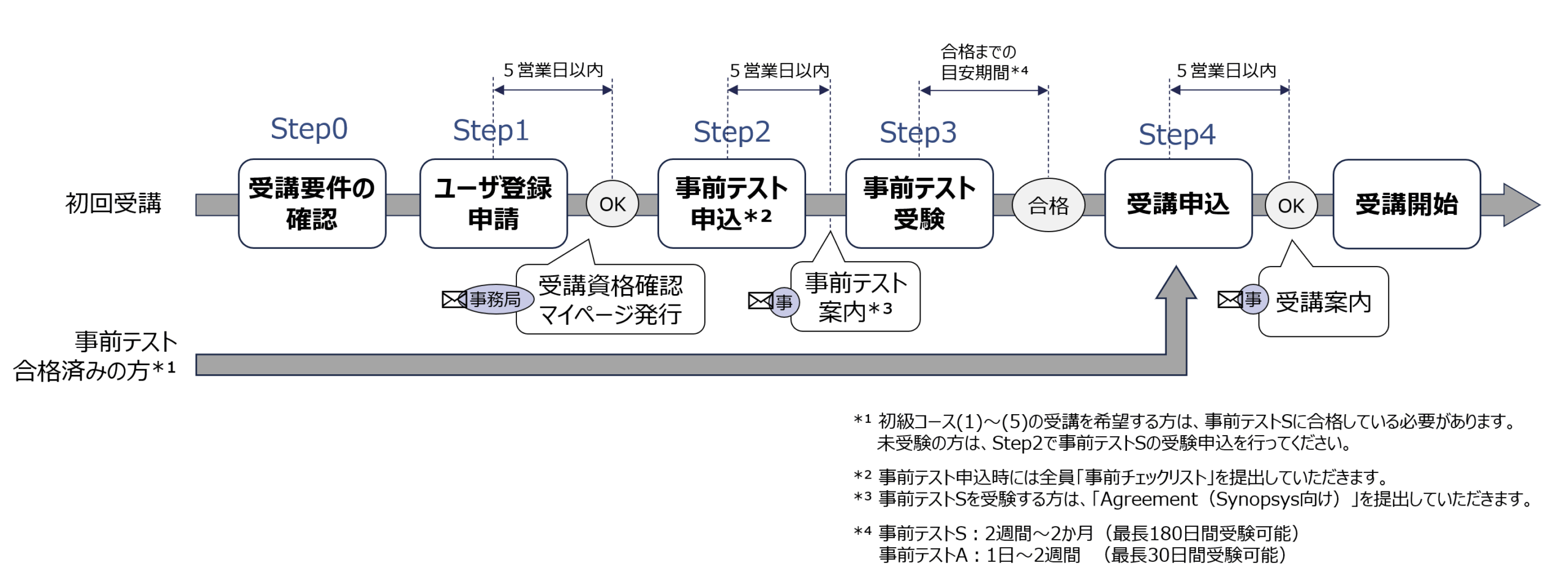

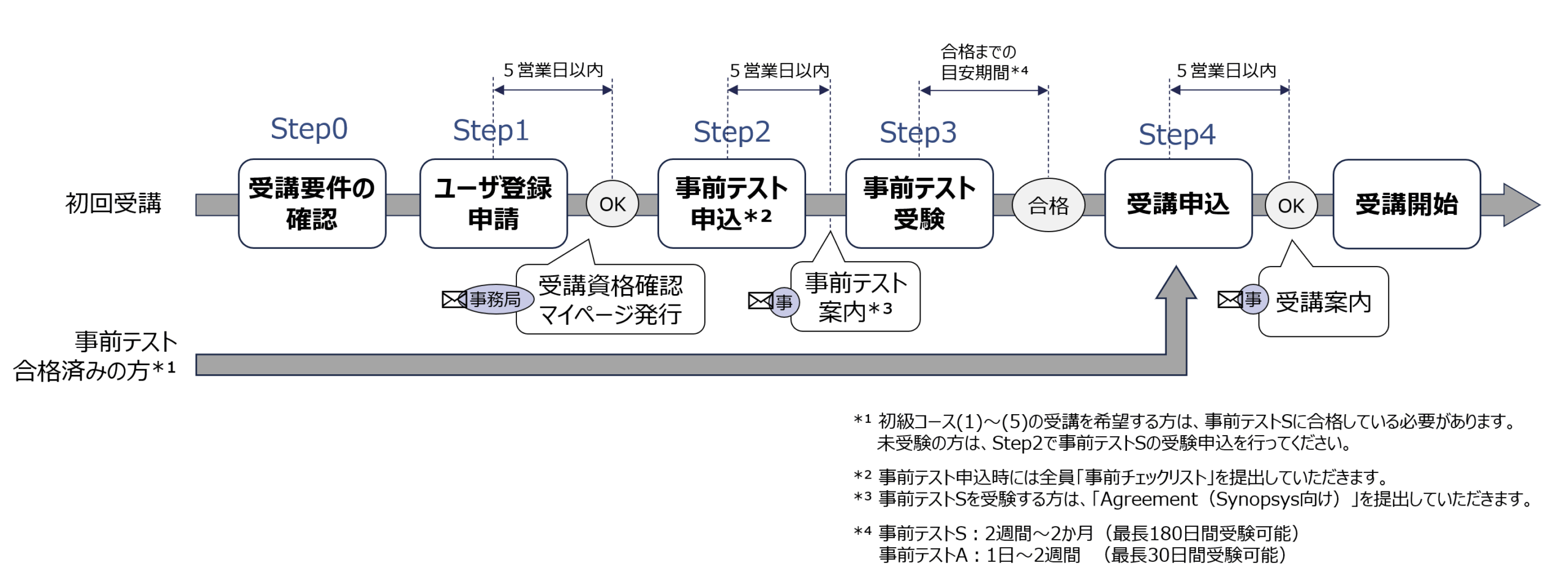

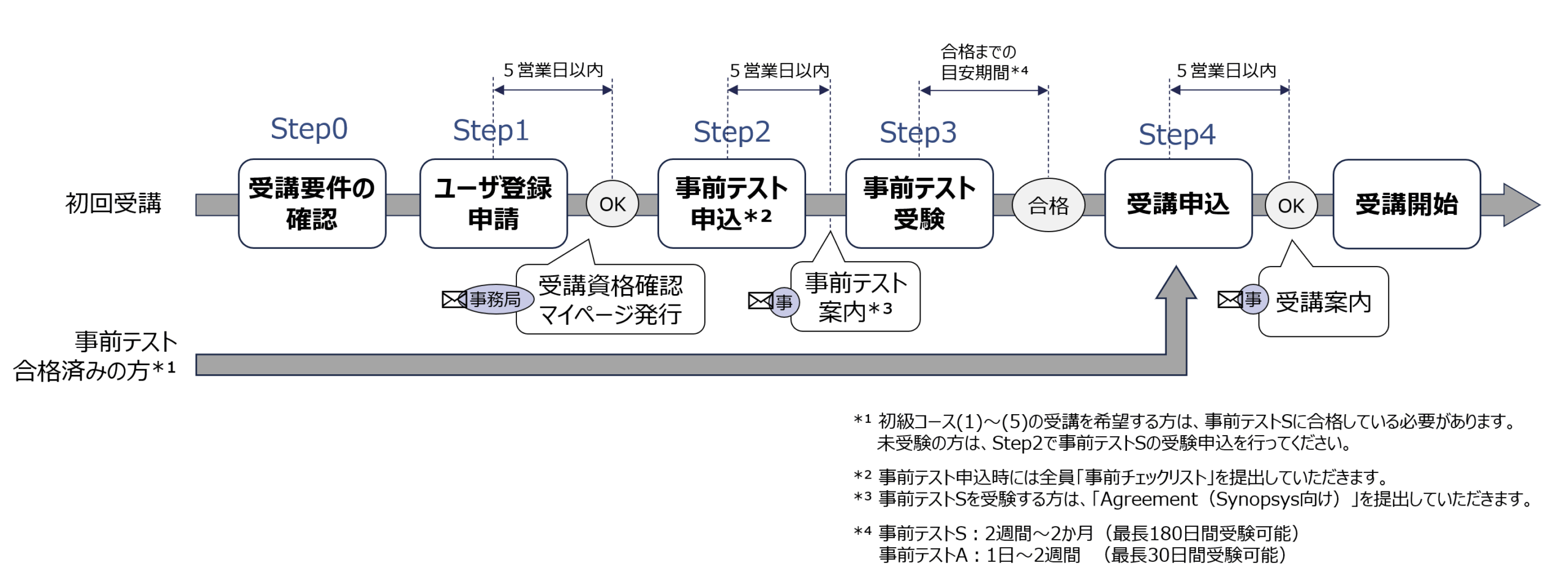

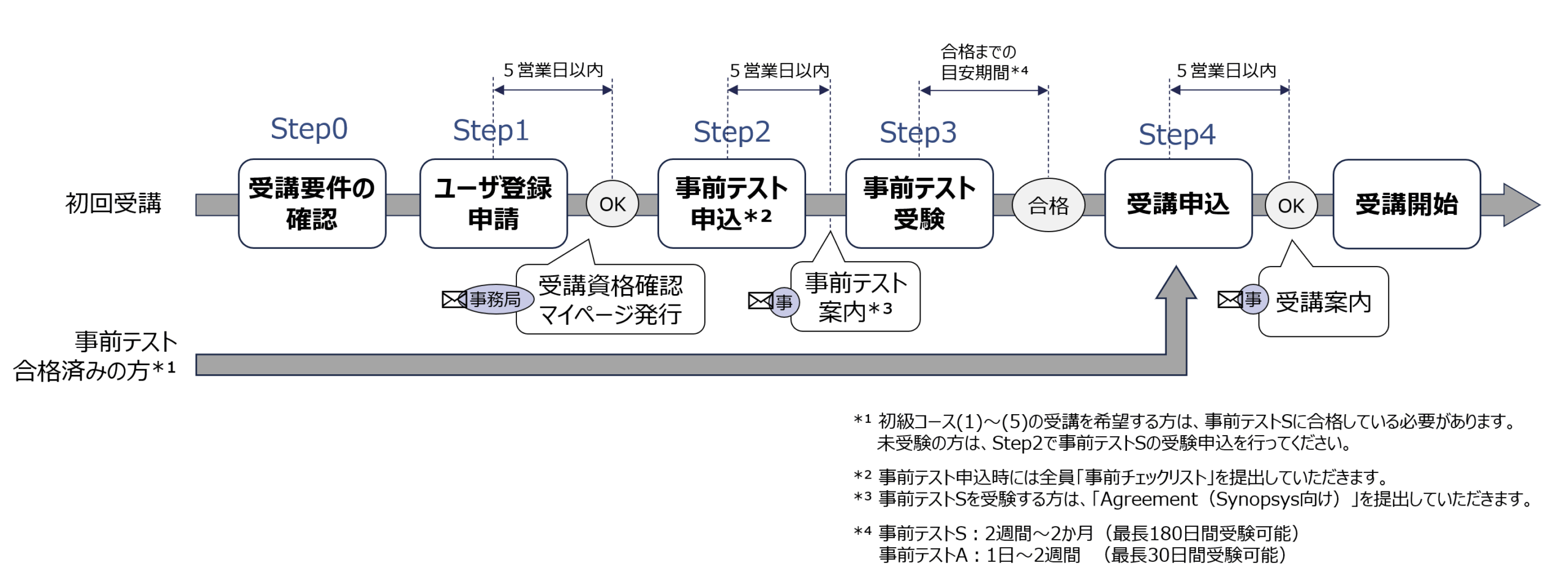

申込手順

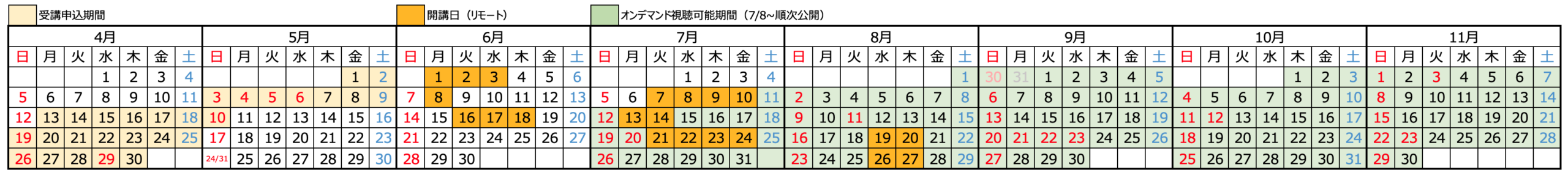

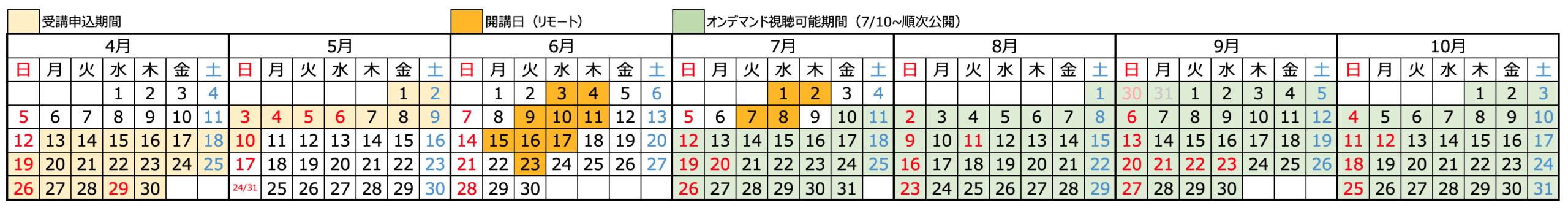

開講スケジュール

2026年5月8日〜8月5日(オンデマンド形式)

うちCloud EDA(演習用ツール)利用可能期間:2026年5月29日〜6月11日

受講申込期間:4月3日〜4月19日

学習目安時間:80時間

受講期間中、ご都合のよい日時に受講いただけます。

※本コースの受講には、事前テストSの合格が必要です(既に合格している場合、再受験は不要)。

※日程は変更の可能性があります。

(2) Design Verificationコース

コース概要

SystemVerilog、SystemVerilog with UVM、VCS® ツールや Verdi® デバッグ環境などの最新EDA ベンダのツールについて、設計検証に必要なすべての知識と実習を提供します。

最先端の商用EDAツールを使用して、デザイン検証に必要なスキルを学習します。Verilog/VHDLとSystemVerilogの基礎、そして、SystemVerilogを用いた、テストベンチ言語とアサーションの使い方などの実践的な設計検証を習得します。さらに、Formal Verification手法を用いたプロパティ記述方法や、UVMを用いた効率的なテスト環境の開発も学習します。

内容

① Design Verification Foundation

この導入トレーニングは、ASIC デザインのモデリングに使用されるハードウェア記述言語Verilog/VHDL とSystemVerilog をリフレッシュするためのものです。

② Design Verification Comprehensive

このコースでは、ハードウェア検証言語としてのSystemVerilog について、実践的な設計例を交えて学びます。

③ SystemVerilog テストベンチ

このコースでは、SystemVerilog テストベンチ言語の主な機能と利点、およびVCS®での使用方法について学習します。

④ SystemVerilog アサーション

このコースでは、SystemVerilog アサーション(SVA)言語の主な機能と利点、およびVCS®ツールでの使用方法について学習します。

⑤ フォーマル検証のためのSystemVerilog

このコースでは、SVA 言語と VC フォーマル用のプロパティの記述方法を学びます。また、アサーション・プロパティを記述する際のグッドプラクティスについても学習します。

⑥ UVM によるSystemVerilog

このコースでは、効率的なテストケース開発を可能にするUVM SystemVerilog テストベンチ環境の開発方法を学びます。

使用ツール

- Synopsys VCS®

- Synopsys Verdi® など

主な対象者

- デザインチームに新規採用された社員

- VLSI設計を始めるキャリア・スターター

- 学士課程、修士課程修了見込みの学生

申込手順

開講スケジュール

2026年5月8日〜8月5日(オンデマンド形式)

うちCloud EDA(演習用ツール)利用可能期間:2026年5月8日〜6月11日

受講申込期間:4月3日〜4月19日

学習目安時間:80時間

受講期間中、ご都合のよい日時に受講いただけます。

※本コースの受講には、事前テストSの合格が必要です(既に合格している場合、再受験は不要)。

※日程は変更の可能性があります。

(3) RTL Synthesisコース

コース概要

このコースでは、RTL 合成に必要なすべての知識を習得し、Design Compiler® NXT、Formality、Fusion Compiler などの最新EDAベンダ製ツールを実際に体験することができます。

最先端の商用EDAツールを使ってRTL合成について学習します。Verilog/VHDLとSystemVerilogの基礎から、Design Compiler® NXTを使ったブロックレベルのRTLデザインの合成、タイミング最適化を習得します。また、Formalityを用いフォーマル検証の手法を習得と、省電力技術、パワードメインの概念についても学びます。さらに、Design Compiler® NXTを使った電力最適化手法も学習します。

内容

① RTL 合成I – 基礎 –

この導入トレーニングは、ASIC デザインのモデリングに使用されるハードウェア記述言語Verilog/VHDL とSynstemVerilog をリフレッシュするためのものです。

② RTL Synthesis II – Comprehensive –

このコースでは、RTL 合成フロー、特にトポグラフィカル・モードでDesign Compiler® NXT を使用してブロックレベルのRTL デザインを合成し、許容可能な配置後のタイミングと混雑度を持つ最終的なゲートレベルのネットリストを生成する方法について学習します。このコースでは、さまざまな合成最適化手法とデザインの制約に関する推奨手法を学びます。

③ Formality

このコースでは、設計検証および失敗した設計のデバッグのためにフォーマル検証フローを適用します。 一般的なハードウェア設計変換のためにFormality を最適化する拡張フローを適用します。パターン解析などのテクニックによりデバッグ能力を高め、検証パフォーマンスを最大化します。

④ UPF の基礎

このコースでは、UPF によって実現できるさまざまな省電力技術の概要と利点を説明し、これらの技術を採用する際の懸念事項や、インプリメンテーションおよび検証スケジュールに影響を与える可能性のある領域を強調します。UPF によるパワードメイン作成の注意点を説明し、最適な結果を得るための「優れたパワー設計分割」の概念を取り上げます。パワードメイン作成におけるトップダウンアプローチと階層的アプローチ、さらに概念的なUPF パワードメイン定義と物理フローとの関連性についても説明します。サプライネット」と「サプライセット」の概念について触れ、それぞれの構成が提供する抽象化レベルについて説明し、SoC ベースまたはIP ベースのエンジニアに、選択したパワー・ドメイン・アーキテクチャを実装および検証するためのメカニズムを提供します。

⑤ Design Compiler® NXT

クロック・ゲーティング、セルフ・ゲーティング、マルチビット・レジスタ・バンキング、低消費電力配置、DesignWare minPower などの電力最適化テクノロジを実行します。

使用ツール

- Synopsys Design Compiler® NXT

- Synopsys Formality

- UPF(Unified Power Format) など

主な対象者

- デザインチームに新規採用された社員

- VLSI設計を始めるキャリア・スターター

- 学士課程、修士課程修了見込みの学生

申込手順

開講スケジュール

2026年5月8日〜8月5日(オンデマンド形式)

うちCloud EDA(演習用ツール)利用可能期間:2026年5月8日〜6月11日

受講申込期間:4月3日〜4月19日

学習目安時間:80時間

受講期間中、ご都合のよい日時に受講いただけます。

※本コースの受講には、事前テストSの合格が必要です(既に合格している場合、再受験は不要)。

※日程は変更の可能性があります。

(4) Design For Testコース

コース概要

このコースでは、ASIC 設計フローにおけるDFT(Design for Testability)について知っておく必要があるすべての情報を提供します。テストの必要性、フォールト・モデリング、テスト挿入手法、自動テストパターン生成(ATPG)、テストカバレッジの概念、および高度なテスト手法をカバーしています。

ASICデザインにおけるテスト容易化設計(DFT)を学習します。先端の商用EDAツールを使ってテスト、故障モデリング、ATPG、テストカバレッジなどを学習します。基本的なDFT概念とATPG生成から、TestMAX™を用いたスキャン挿入やDFTルールチェック、さらに、TestMAX™ Advisorを使ったRTLのテスト容易性解析や、ATPGでのテストパターン生成について学びます。コースは、Fusion CompilerによるDFT合成フローもカバーしています。

内容

① Design For Test I

このイントロダクションでは、IC のテスト、ウェハーソーティング、欠陥-故障マッピング、故障モデリング、故障シミュレーション、DFT テスト可能性の概念、ATPG 生成、および高度なテスト技術を含むDFT について説明します。

② Design For Test II:Comprehensive

このコースでは、 Synopsys製TestMAX™ Advisor を使用したDFT の使用方法、DFT とDiagnosis を使用した設計フローのスキャン、故障シミュレーション、TestMAX™ DFTを使用したテスト挿入について学習します。

③ Design For Test III:Synopsys製ツールによるジャンプスタート

a) TestMAX™ DFT:ジャンプスタート

TestMAX™ DFT を使用して、ゲートレベルのDFT ルールチェック、DFT DRC ルール違反の修正、トップダウンおよびボトムアップフローを使用したインサートスキャン、ダウンストリームツールへの結果のエクスポートを学習します。

b) TestMAX™ Manager ジャンプスタート

DFTMAX スキャン・コンプレッション、オンチップ・クロック・コントローラなどのDFT IP を生成し、ユーザRTL にインスタンス化するためのTestMAX™ Manager フローの概要を説明します。

c) TestMAX™ SMS ジャンプスタート

メモリは複雑で、よく構造化されています。メモリのテストには、その機能を論理的にも物理的にも深く理解する必要があります。各メモリは異なるコンフィギュレーションを持ち、メモリのテストに使用するテスト・メカニズムは、そのアーキテクチャに応じてカスタマイズする必要があります。このトレーニングでは、最新EDA ベンダのTestMAX™ Star Memory System(SMS)を使用してこの要件に対応する方法について説明します。このトレーニングでは、さまざまなメモリ・コンフィギュレーションに対応するSMS アーキテクチャと、SoC レベルからこれらのメモリにアクセスする方法について簡単に説明します。

④ TestMAX™ DFT

最新EDA ベンダ製 TestMAX™ DFT を使用したRTL およびゲートレベルのDFT ルールチェック、DFT DRC ルール違反の修正、トップダウン/ボトムアップフローを使用したスキャン挿入の方法を詳しくご紹介します。論理(Design Compiler®)ドメインでのボトムアップ・スキャン挿入フローなど、数百万ゲートの大規模SoC 設計をサポートするために不可欠なテクニックをご紹介します。

⑤ TestMAX™ Advisor

最新EDA ベンダ製のTestMAX™ Advisor(旧称SpyGlass® DFT)を使用してRTL テスト容易性解析を実行し、設計サイクルの初期段階でRTL の微調整を行う方法をご紹介します。これにより、デザイン・スキャンのレディネスとテストのロバスト性を検証し、フォルトおよびテストカバレッジの目標を達成することができます。

⑥ TestMAX™ ATPG

TestMAX™ ATPG を使用して、TestMAX™ DFT または他のツールで作成されたスキャンゲートレベルのデザインを指定し、スタックアットフォルトのテストパターンを生成する方法を学習し、STIL を使用したテストプロトコルとテストパターンのタイミングについて説明します。

⑦ Fusion Compiler DFT 合成

このコースでは、Fusion Compiler を使用したスキャン合成について学びます。コースは、スキャンテストの基礎、Fusion Compiler でサポートされるスキャン合成フロー、デザインルールチェックの実行とデバッグから始まり、ブロックレベルでのスキャンチェーンの構築へと進みます。

使用ツール

- Synopsys TestMAX™ DFT

- Synopsys TestMAX™ Advisor

- Synopsys Fusion Compiler など

主な対象者

- VLSI設計チームの新卒エンジニア

- VLSI領域でキャリアをスタートさせるプロフェッショナル

- 学士課程、修士課程修了見込みの学生

申込手順

開講スケジュール

2026年5月8日〜8月5日(オンデマンド形式)

うちCloud EDA(演習用ツール)利用可能期間:2026年5月29日〜6月4日

受講申込期間:4月3日〜4月19日

学習目安時間:80時間

受講期間中、ご都合のよい日時に受講いただけます。

※本コースの受講には、事前テストSの合格が必要です(既に合格している場合、再受験は不要)。

※日程は変更の可能性があります。

(5) Analog & Mixed Signal (AMS) Circuit and Layout Designコース

コース概要

このコースには、アナログ/ミックスド・シグナル(AMS)回路とレイアウト設計の流れについて知っておく必要があるすべてが含まれています。

アナログおよびミックスドシグナル(AMS)回路とレイアウト設計の基礎を学習します。AMS回路設計の基本要素やトポロジ、安定性解析を学び、VDSMアナログ設計やPDKの使い方、Custom Compiler™を用いた設計手法も習得します。さらに、Custom Compiler™を使った回路図の設計、レイアウト編集、協調設計フローに加え、PrimeSim SPICEを使ったシミュレーションと解析についても学習します。

内容

①AMS の回路とレイアウト設計

アナログ回路の基礎、回路素子(抵抗、コンデンサ)、基本回路トポロジ(抵抗としてのMOSFET 構造、増幅器、PLL、データ・コンバータ)、それらの等価モデル、電流源、フィードバック理論、ディジェネレーション、等価モデル・パラメータ、回路設計手法、安定性解析について、例題を交えて解説します。

②AMS 回路とレイアウト設計

このコースでは、VDSM アナログ設計の基礎と使用部品の回路動作について学びます。オペアンプ、PLL、パッシブデバイスを含むアナログ機能とコンポーネントをカバーします。また、PDK の紹介、スタンダードセル、インバータ、オペアンプのリファレンス回路の設計も行います。Custom Compiler™ ツールを使用した回路設計のデモンストレーションも含まれます。また、ミックスドシグナル回路設計の流れも紹介します。

③カスタムコンパイラFoundation

Custom Compiler™ は、カスタム・デジタル、アナログ、ミックスドシグナル集積回路(IC)の設計に必要なすべての機能を備えた完全な設計プラットフォームです。Custom Compiler™ 入門コースでは、Custom Compiler™ の起動方法と基本機能の使用方法を学習します。

④カスタムコンパイラ回路図入力

このコースでは、Custom Compiler™ の設計手法を学びます。Custom Compiler™ ツールを使用してアナログ回路設計と検証を行います。また、Custom Compiler™の協調設計フローについても学習します。

⑤カスタムコンパイラ基本的なレイアウト設計

このコースでは、Custom Compiler™ Layout Editor ツールやその他のCustom Compiler™ ツール、アシスタントを使用した基本的なレイアウト編集機能について学習します。

⑥PrimeWave™ 設計環境におけるPrimeSim SPICE シミュレーションと解析

このコースでは、PrimeWave™ 設計環境におけるPrimeSim SPICE シミュレーションと解析を使用したアナログ回路シミュレーションとデバッグ手順について学習します。

使用ツール

- Synopsys Custom Compiler™

- Synopsys PrimeSim SPICE など

主な対象者

- VLSI設計チームの新卒エンジニア

- VLSI領域でキャリアをスタートさせるプロフェッショナル

- 学士課程、修士課程修了見込みの学生

申込手順

開講スケジュール

2026年5月8日〜8月5日(オンデマンド形式)

うちCloud EDA(演習用ツール)利用可能期間:2026年5月22日〜6月11日

受講申込期間:4月3日〜4月19日

学習目安時間:80時間

受講期間中、ご都合のよい日時に受講いただけます。

※本コースの受講には、事前テストSの合格が必要です(既に合格している場合、再受験は不要)。

※日程は変更の可能性があります。

(6) PCB Design and Analysisコース

コース概要

本コースでは、PCB設計やカスタム設計にまつわるCadenceのツール群を実践的に用いて、各種スキルを習得することのできる講習を実施します。

最先端の商用EDAツールを用いてシステム全体としてのPCB設計やアナログシミュレーションなどのスキルを学びます。Allegro® X System CaptureやAllegro® X PCB Editorの基礎から中級技術、PSpice®を使ったアナログシミュレーション、Sigrity™ソフトウェアを使った高速設計やパワーデリバリーネットワークの解析までをカバーしており、各ツールの操作方法を実践的に学び、設計フロー全体を習得することができます。

内容

PCB設計、解析ツール群の基本機能の講習を実施します。これにより、PCBの回路、レイアウト設計と解析環境のスキルを習得することができます。

① Allegro® X System Captureフロント・トゥ・バック フロートレーニング

このコースでは、System Captureを使用してボードレベルの回路図設計を作成します。System Captureと設計フロー内の他のツール、特にAllegro® PCBエディタとの統合について学びます。回路図の作成からボードレイアウトまでの設計フローを追います。

② Allegro® X System Capture 基礎トレーニング

このコースでは、Allegro® X System Captureの基礎を学びます。フラットなマルチシートの回路図を作成したり、他の設計からシートをコピーしたり、既存プロジェクトを基に新しいプロジェクトを作成したりします。また、設計変更プロセスも学びます。

③ PSpice® Trainingを使用したアナログシミュレーショントレーニング

PSpice®を使用したアナログシミュレーションコースでは、基本的な設計入力からシミュレーションまでの基礎を学び、DCバイアスシミュレーション、過渡解析、スイープシミュレーションなどを実行します。さらに、アナログ回路、変圧器、デジタル回路、アナログ/デジタル混合回路、およびストレス解析のシミュレーションも行います。また、高度な解析として、感度解析、モンテカルロ解析、最適化、ストレス解析、パラメトリックプロッタもカバーします。

④ Allegro® X PCB エディタ 基礎技術トレーニング

このコースは2部シリーズの最初のコースです。このコースを終了した後、Allegro® PCBエディタ中級技術コースを受講することが推奨されます。Allegro® X PCBエディタ基本技術コースには、ロジックとネットリストデータの読み込みから基板製造/NCデータの生成まで、PCB設計の基本的なステップが含まれています。タスク指向の実習では、インタラクティブおよび自動ツールの組み合わせの使用方法を教えます。このコースには、Allegro® Xデザイナー レイアウト ライセンス以上が必要です。

⑤ Sigrity™ Auroraトレーニング

このコースでは、Sigrity™ Auroraソフトウェアを使用して、高速回路設計のための設計ルールを開発します。トポロジーテンプレートを用いて設計に物理的および電気的制約を追加します。これらの制約は、プリント基板上のネットの配線を実施します。配線前および配線後の信号シミュレーションを実行し、PCBの反射、クロストーク、IR Drop、その他の高速回路設計の要因を分析します。

⑥ Sigrity™, PowerDC™ および OptimizePI™ トレーニング

Sigrity™ PowerDC™およびOptimizePI™は、高速プリント基板(PCB)におけるパワーデリバリーネットワークの解析手法を提供します。パワーデリバリーネットワークの設計には、電圧レギュレータモジュール、デカップリングコンデンサ、電源/グランドプレーンが含まれます。このコースでは、Sigrity™ Power Integrity Suiteソフトウェアを使用して、高速回路の動作をサポートするための安定した電力分配システムを分析します。

使用ツール

- Cadence Allegro® X Design Entry HDL

- Cadance PSpice®

- Cadance Sigrity™ Aurora など

主な対象者

- Linux/Windowsのオペレーション経験がある方

- 電機システム設計の基礎知識を習得している方

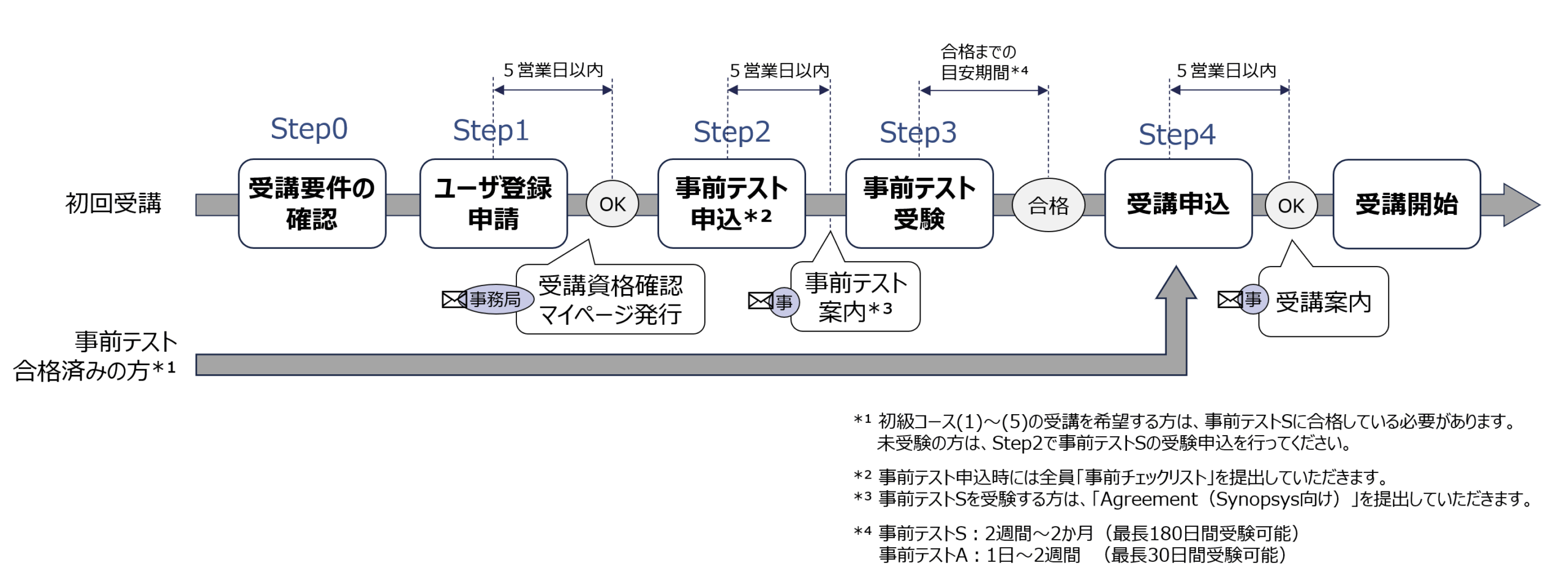

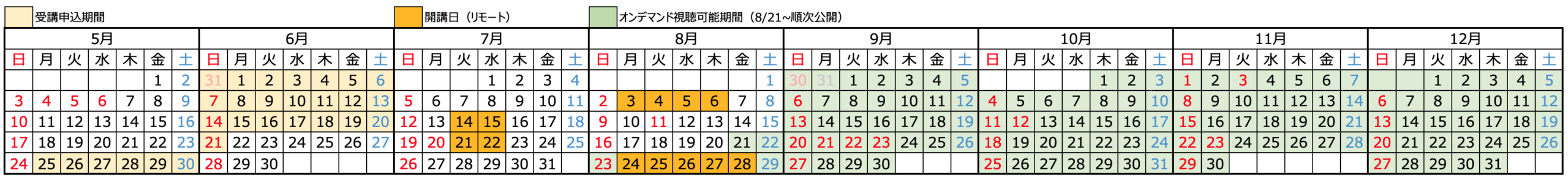

申込手順

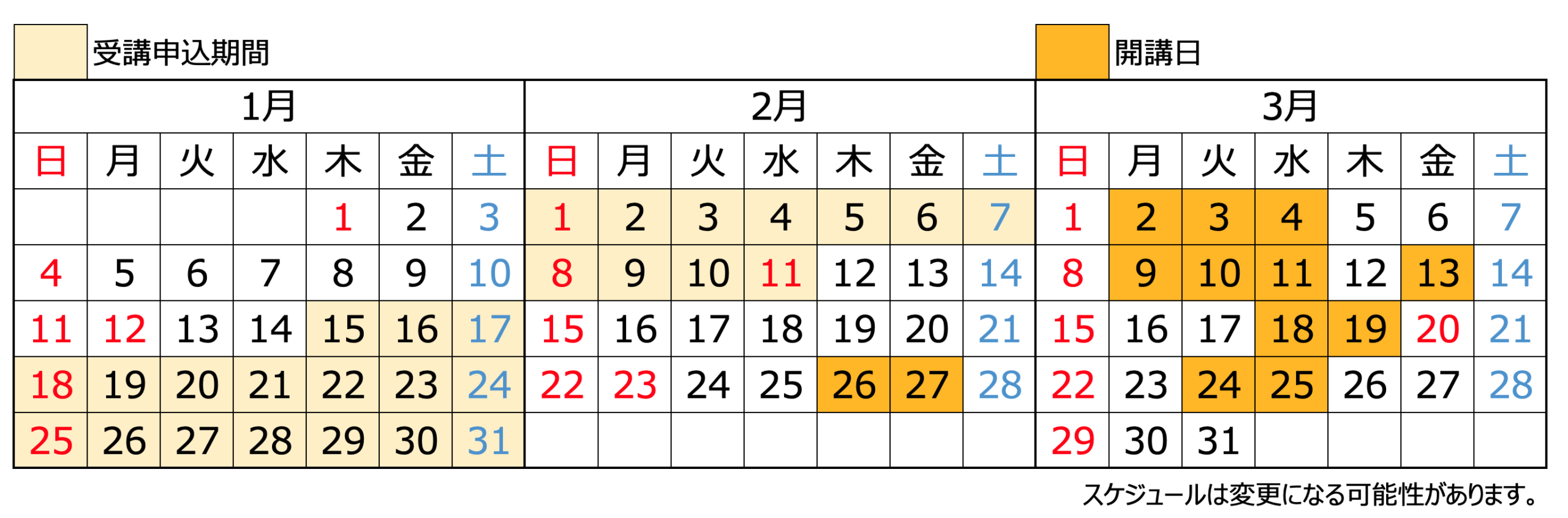

開講スケジュール

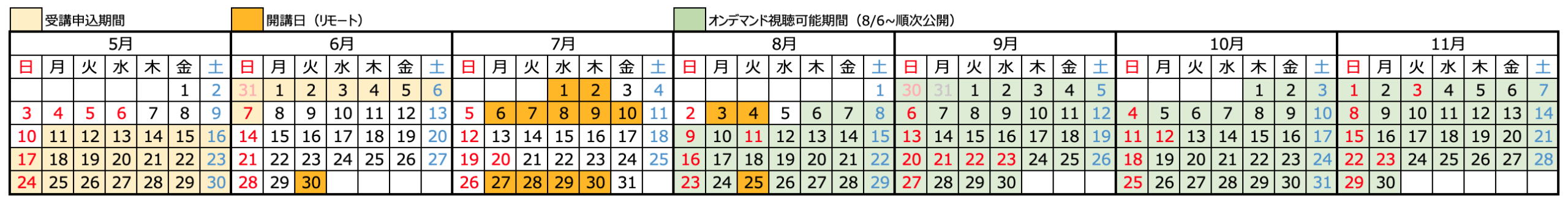

2026年6月30日〜8月25日(リモート形式)

8月6日〜11月30日(オンデマンド形式)

受講申込期間:2026年5月11日〜6月7日

学習目安時間:80時間

<受講方法について>

リモート(決まった日時に受講)、オンデマンド(期間中都合の良い時間に受講)を、各セクションごとに自由にお選びいただけます。

リモート:原則10:00-17:00 、Zoomでの開催です。リアルタイムで質疑応答も可能ですので、ぜひご検討ください。

オンデマンド:リモート講義の動画を、記載の期間から順次公開します(リモート参加の場合も視聴可)。期間中は何度でも受講が可能です。

※本コースの受講には、事前テストの合格が必要です(既に合格している場合、再受験は不要)。

※日程は変更の可能性があります。

(7) Custom IC, Analog, Microwave and RF Designコース

コース概要

本コースでは、カスタム設計にまつわるCadenceのツール群を実践的に用いて、各種スキルを習得することのできる講習を実施します。

最先端の商用EDAツールを使用して、カスタムIC設計やアナログ、RF設計に必要なスキルを学びます。Virtuoso® Schematic EditorやVirtuoso® ADE Explorerを使った回路設計・シミュレーションの基礎から、Spectre®シミュレータによる解析やVirtuoso® Layout Suiteでのレイアウト設計、さらに寄生抽出や高速設計の検証までをカバーしています。これにより、総合的なアナログおよびカスタムIC設計のスキルを習得することができます。

内容

カスタム設計ツール群の基本機能の講習を実施します。これにより、アナログ、RF ICの回路、レイアウト設計、解析環境のスキルを習得することができます。

① Virtuoso® Schematic Editorトレーニング

Virtuoso® Schematic Editorコースでは、Cadenceのシミュレーションおよびレイアウトツールスイートと組み合わせて使用するための回路図を作成および編集する方法を学びます。LおよびXLツールスイートの機能にアクセスし、インスタンスを配置し、回路図を配線し、マルチレベル回路図のための階層設計の概念を使用します。その後、Verilog InおよびSPICE Inトランスレータを使用してネットリストおよびシンボルを生成します。

さらに回路ネットリストを作成し、シミュレーションを実行します。

Schematic XLでは、Constraint EditorおよびCircuit Prospectorアシスタントを使用して設計ルールを追加します。また、継承接続を作成し、回路図からレイアウトインスタンスを生成します。Schematic MappingまたはAnalog Schematic Migrationの作成も行います。

② Virtuoso® Visualization and Analysisトレーニング

このコースでは、Virtuoso® Visualization and Analysisツールを使用して、Virtuoso® ADE Explorerからのシミュレーション結果を閲覧、評価、分析、およびプロットします。このツールは、単独のツールとして、またADE Explorer内の統合されたグラフアシスタントとして使用します。Results Browserを使用してシミュレーションデータベースにアクセスし、Calculatorを使用して情報を後処理します。ADE ExplorerのDirect Plotフォームを使用して、波形ビューアに直接解析関連情報をプロットします。

③ Virtuoso® ADE ExplorerおよびAssemblerトレーニング

a) S1: ADE Explorerおよび単一テストコーナ解析トレーニング

このコースでは、Virtuoso® ADE Explorerツールを使用してアナログ設計のシミュレーションをセットアップおよび実行し、ユーザがセットアップ中に記載したデザイン変数に従い、システムパラメータのスイープを行い、単一のテストベンチを使用してSpectre®をシミュレータとしてを用いてシミュレーションを実行し、その結果をVirtuoso®Visualization and Analysis波形ビューアで表示します。

b) S2: ADE Assemblerおよびマルチテストコーナ解析トレーニング

このコースでは、Virtuoso® ADE Assemblerを使用して、アナログ/ミックスドシグナル設計のためのシミュレーションをセットアップし実行します。マエストロcellviewを使用して、複数のテストに対して、設定、実行し、結果をプロットします。また、シミュレーション履歴を確認および管理します。

c) S3: 変数のスイープおよびコーナー解析トレーニング

このコースでは、Virtuoso® ADE Assemblerを使用してアナログ設計のシミュレーションを実行します。ツール内のアシスタントを使用して、デザインをパラメータ化し、グローバルおよびローカル変数のスイープを作成して、複数の設計ポイントおよび回帰をシミュレートします。また、コーナー解析をセットアップおよび実行し、コーナーやスイープ全体でデータを測定するために式を使用します。

d) S4: モンテカルロ解析、リアルタイムチューニング、およびランプラン トレーニング

このコースでは、ADE Explorer内でモンテカルロ解析をセットアップし、不一致のバリエーションを考慮し、目標の達成度に基づいて実行を自動停止する方法を学びます。成功したポイントの歩留まり情報をフィルタリングし、ヒストグラムをプロットし、統計パラメータを出力します。リアルタイムチューニングアシスタントを使用して、個別のシミュレーション実行後にADE Explorerコックピット内の結果を動的に更新します。また、ADE Assemblerのランプランアシスタントを使用して、設計の検討事項を確認するためのミニランプランを作成することを学びます。

④ Spectre® シミュレータ基礎

a) S1: Spectre® 基本トレーニング

このコースはSpectre®シミュレータ基礎シリーズの一部です。このコースでは、Spectre® Netlist言語の構文を指定し、コマンドラインおよびADE Explorer環境からSpectre® Classicシミュレータを使用して高速かつ正確なアナログシミュレーションを実行する方法を学びます。Spectre®シミュレータ設定を行い、言語構文を指定して、Virtuoso® Visualization and Analysisツールを使用して波形をプロットし、シミュレーション結果を分析します。ネットリスト制御ステートメントを使用して、Spectre®コマンドラインシミュレーションの流れを制御する方法も学びます。

Spectre®コマンドラインオプションを探索し、出力フォーマットを指定する方法や、ネットリストを暗号化して機密情報を保護する方法を学びます。さらに、Spectre® ClassicシミュレータのSPICEシミュレーション言語との互換性を確認し、SPICEベースのネットリストを使用してSpectre®コマンドライン環境でシミュレーションを実行する方法を学びます。また、ADE Explorer環境でSpectre®シミュレーションをセットアップし、実行します。

b) S2: 大信号解析トレーニング

このコースはSpectre®シミュレータ基礎シリーズの一部です。このコースでは、Spectre® Circuitシミュレータを使用して、コマンドラインおよびADE Explorer環境の両方でDCおよび過渡の大信号解析を実行する方法を学びます。コアモジュールの1つであるDC解析では、DC動作点(OP)およびバイアス条件の計算方法を学び、ニュートン・ラプソン反復法を使用して非線形方程式の解を求めます。また、DC動作点およびDCスイープ解析をセットアップして実行し、DCパラメータがシミュレーションの精度や収束にどのように影響するかを理解します。

別のコアモジュールである過渡解析では、過渡解析の収束基準を検討し、数値積分法を設定して過渡シミュレーションの問題点を特定します。さらに、局所誤差(LTE)の意味を理解し、過渡解析の時間ステップを制限し、データ削減およびデータ圧縮技術を使用して出力データを制御する方法を学びます。過渡解析中に小信号解析を実行し、過渡解析中にパラメータをスイープする方法も学びます。

c) S3: 小信号解析トレーニング

このコースはSpectre®シミュレータ基礎シリーズの一部です。Spectre® Circuitシミュレータとその対応するオプションを使用して、AC解析、伝達関数(XF)、ノイズ、安定性(STB)、ループファインダー(LF)、極零点(PZ)、Sパラメータ(SP)、DCマッチ、ACマッチ、フーリエ解析、感度解析、およびスイープ解析の結果を分析します。コマンドラインおよびADE Explorer環境の両方を使用して、回路例のシミュレーションをセットアップおよび実行します。すべてのシミュレーション結果は、Virtuoso® Visualization and Analysisツールを使用して分析およびプロットされます。

d) S4: 測定記述言語トレーニング

このコースはSpectre®シミュレータ基礎シリーズの一部です。このコースでは、Spectre® Circuitシミュレータの測定記述言語(MDL)を使用して、シミュレーションおよびデータ解析の生産性を向上させる方法を学びます。エイリアス測定を使用して、分析を実行し、回路の性能に関する情報を抽出します。また、MDLがどのようにさまざまな入力、出力、ツールと相互作用するかを学び、MDL測定を作成して再利用し、最終的にSpectre® MDLをスタンドアロンおよびバッチモードで実行して、*.measure出力ファイルに測定値を表示する方法を学びます。

⑤ Virtuoso® Layout 設計基礎トレーニング

このコースでは、Virtuoso® Studio Layout Suite 環境でデザインを操作するための基本的なテクニックを学習します。セルレベルのデザインを作成および編集します。インスタンスを作成・配置して、カスタム物理デザインの階層を構築します。物理デザインの選択、ナビゲート、検索、ハイライト、編集、作成を支援するユーザーインターフェースとユーザーインターフェースアシスタントの基本を学習します。デバイスレベルでセルを作成するための基本的な方法を学習します。長方形、ポリゴン、パス、ワイヤ、セルインスタンスを作成します。これらのシェイプをデザインルール仕様に合わせて編集します。階層を移動してインプレイス編集するか、セル自体に降りて編集します。下位レベルのセルを表す新しいセルを作成し、これまでのモジュールで学習したスキルを使用してトップレベルのブロックデザインを作成します。

⑥ Virtuoso® Connectivity-Driven Layout Transition トレーニング

このコースでは、Virtuoso® Layout Suite Lを使用した完全に独立したレイアウト環境から、Virtuoso® Layout Suite XL、GXL、EAD、およびEXLで提供されるフルコネクティビティと自動化に移行する方法を学びます。このコースは、IC6.1.8およびICADVM20.1バージョンに基づいています。このコースでは、両方のストリーム(IC618およびICADVM20.1)の自動化の強化とその利点の概要に焦点を当てています。

⑦ Virtuoso® Layout Pro

a) T1: 環境と基本コマンドトレーニング

このコースでは、IC 23.1環境で利用可能な機能を使用します。Virtuoso® Layout Suiteを使用してレイアウトを作成する際に、作業環境をカスタマイズしてエクスペリエンスを向上させる方法を学びます。また、ズームの必要性を最小限に抑えながら編集操作を行うための新しいユーザインターフェース機能を活用します。

b) T2: 作成及び編集コマンドトレーニング

このコースでは、Virtuoso® Layout Suiteに導入された高度な機能の使用方法を学びます。レイアウト形状の作成を自動化するためのコマンドに精通し、設計内のオブジェクトをより効率的に管理できるコマンドを学びます。また、パスとワイヤの違いについて学び、日常のレイアウト作業でワイヤをどのように活用できるかを理解します。

MDL(Measurement Description Language)がどのように多様な入力、出力、ツールと連携するかを調べます。また、MDL測定を作成し再利用する方法、さらにSpectre® MDLをスタンドアロンおよびバッチモードで実行して、測定値を*.measure出力ファイルで観察する方法を学びます。ADE Explorer環境内でMDLファイルを使用する方法も調べます。

⑧ Pegasus Verification System トレーニング

このコースは、ユーザレベルの物理設計検証のために設計されています。設計内のレイアウトエラーを見つけてデバッグするために、DRC、LVS、ERC、PERC、FastXOR、およびiPegasusチェックを実行します。オプションを設定し、検証を実行し、Pegasus Results Viewerを使用して違反箇所を特定、分析し、修正します。LVSチェックでは、Interactive ShortsLocator(ISL)、プロービングフォーム、およびStamping Conflict Debuggerなどの機能を使用して、ショートやスタンピングの競合をデバッグします。FastXORを使用して、ストリームファイルを既存のOpenAccessセルビューと比較します。

このコースでは、レイアウト設計アクセスにVirtuoso® Layout Suiteを使用し、Pegasus Verification Systemが統合されています。

⑨ Quantus™ トランジスタレベル抽出

a) T1: 概要および技術セットアップトレーニング

このコースでは、次世代の寄生抽出ソリューションであるCadenceのQuantus™ Extraction Solutionについてユーザレベルの体験を提供します。設計完了における寄生抽出の課題を学び、Quantus™ Extraction Solutionを使用してそれらに対処する方法を学びます。また、Quantus™ Extraction Solutionが設計フローにどのように適合するかを確認し、抽出環境を設定します。その後、Quantus™技術ディレクトリ構造を分析し、抽出機能を探索し、GUIモードおよびコマンドラインモードの両方で寄生抵抗、容量、およびインダクタンスを効果的に抽出する方法を学びます。このコースでは、Virtuoso® Layout SuiteおよびPegasus Verification Systemと連携してQuantus™を使用します。Quantus™ Extraction Solutionは、簡単にアクセスできるようにVirtuoso®のメニューバーに統合されています。

b) T2: 寄生抽出トレーニング

このコースは、次世代の寄生抽出ソリューションであるCadenceのQuantus™ Extraction Solutionに関するユーザレベルの体験を提供します。最初に、Pegasus-Quantus™データフローの概要を学び、実際の抽出作業に進みます。GUIモードまたはコマンドラインで抽出環境を設定し、Quantus™ Extraction Solutionの各機能や設定を詳しく探索します。

このコースでは、ランダムウォークフィールドソルバー、適応メッシング、スプリットワイドMOS抽出、階層抽出、マルチコーナー抽出、リダクションコントロール、そしてAdvanced Virtual Metal Fill(VMF)などの機能を学びます。特定の抽出機能では、PEEC(Partial Element Equivalent Circuit)モデルを用いた寄生インダクタンス抽出や、Substrate Noise Analysis(SNA)を使用した寄生基板抽出についても学びます。

このコースでは、Virtuoso® Layout SuiteおよびPegasus Verification Systemと連携してQuantus™を使用します。Quantus™ Extraction Solutionは、簡単にアクセスできるようにVirtuoso®のメニューバーに統合されています。

c) T3: 抽出ビューフローと高度な機能トレーニング

このコースでは、次世代の寄生抽出ソリューションであるCadenceの Quantus™ Extraction Solutionに関するユーザレベルの体験を提供します。まず、Quantus™の高度なノード設計ソリューションを探索します。FinFET、3D-IC、ダブル/マルチパターニング(DPT/MPT)設計における抽出の課題を分析し、それらに対応するQuantus™抽出ソリューションを確認します。また、カラー抽出フローとノンカラー抽出フローの利点と欠点を確認し、悲観性の削減を行います。Quantus™を使用して7nm DPTモデリング、シフトコーナーフローを実行し、TSVとマイクロバンプを使用した3D-IC設計を探索します。最後に、Voltus™-Fiカスタムパワーインテグリティソリューションを使用したトランジスタレベルのEMIR解析フローと、その高度な機能を確認します。Quantus™抽出ソリューションは、Virtuoso®環境に統合されています。

使用ツール

- Cadence Virtuoso® Schematic Editor

- Cadance Virtuoso® Visualization and Analysis

- Cadance Virtuoso® ADE Explorer など

主な対象者

- Linuxのオペレーション経験がある方

- アナログ設計の基礎知識を習得している方

申込手順

開講スケジュール

2026年6月1日〜8月27日(リモート形式)

7月8日〜11月30日(オンデマンド形式)

受講申込期間:4月13日〜5月10日

学習目安時間:115時間

<受講方法について>

リモート(決まった日時に受講)、オンデマンド(期間中都合の良い時間に受講)を、各セクションごとに自由にお選びいただけます。

リモート:原則10:00-17:00 、Zoomでの開催です。リアルタイムで質疑応答も可能ですので、ぜひご検討ください。

オンデマンド:リモート講義の動画を、記載の期間から順次公開します(リモート参加の場合も視聴可)。期間中は何度でも受講が可能です。

※本コースの受講には、事前テストの合格が必要です(既に合格している場合、再受験は不要)。

※日程は変更の可能性があります。

(8) Digital Design and Signoffコース

コース概要

本コースでは、デジタル設計にまつわるCadenceのツール群を実践的に用いて、各種スキルを習得することのできる講習を実施します。

最先端の商用EDAのRTL-to-GDSIIフローに基づいてデジタル設計を実行し、検証するスキルを学びます。Genus™ Synthesis Solution、Innovus™ Implementation System、Tempus™ Timing Signoff Solutionなどのツールを用いて、設計のパワー、パフォーマンス、面積(PPA)の最適化や階層的な実装、タイミング解析を行います。さらに、Conformal® Equivalence Checkerを使った機能検証を通じて、設計の正確さを確保し、問題点をデバッグする方法を学習します。

内容

デジタル設計ツール群の基本機能に関する講習を行います。これにより、SoC(RTL 以降)のインプリメンテーション、サインオフ環境のスキルを習得することができます。

① 最新EDA ベンダ RTL-to-GDSII フロートレーニング

このコースはユーザレベルの物理設計検証用に設計されています。DRC、LVS、ERC、PERC、FastXOR、およびiPegasus チェックを実行して、設計内のレイアウトエラーを見つけ、デバッグします。オプションを設定して検証を実行し、Pegasus Results Viewer を使用して違反を特定、分析し、修正します。LVS チェックでは、Interactive Shorts Locator(ISL)、プロービングフォーム、およびスタンピング競合デバッガなどの機能を使用してショートやスタンピング競合をデバッグします。FastXOR を使用して、ストリームファイルを既存のOpenAccess セルビューと比較します。

このコースでは、Virtuoso® Layout Suite がレイアウト設計アクセスに使用され、PegasusVerification System が統合されています。

② Genus™ Synthesis Solution with Stylus Common UI トレーニング

このコースでは、最新EDA ベンダ Genus™ Synthesis Solution with Stylus Common UI の特徴について学びます。このツールは、次世代の合成機能(大規模並列処理、高い相関性、RTL 設計に焦点を当てた最適化、アーキテクチャレベルのPPA:パワー、パフォーマンス、面積の最適化)を備えており、SoC 設計における生産性のギャップを埋めます。

このコースでは、設計に制約を与えるための様々な技術、スタティックタイミング解析の実行、データパスロジックの評価、物理合成の実行、低消費電力構造の最適化、DFT(テスト容易化設計)制約の解析、およびGenus™ Stylus Common UI 内での他のツールとのインターフェース方法を学びます。また、論理最適化の手順を理解し、デジタル設計のためのさまざまな入力および出力ファイルを生成する手順を習得します。

さらに、仕様に基づいた設計の完全な合成フローを実行し、面積、タイミング、電力の観点で最適化する方法を学びます。設計データベースのクエリ方法や合成フローに必要な属性の設定方法も学びます。さらに、Genus™ におけるマルチモード・マルチコーナー(MMMC)合成フローを探索し、Flowkit およびUnified Metrics の機能についても学びます。

③ Innovus™ ブロック実装と Stylus Common UI トレーニング

このコースでは、最新EDA ベンダ Innovus™ Implementation System ソフトウェアをStylus Common User Interface(UI)を使用して、設計の最適なパワー、パフォーマンス、面積(PPA)を実現する方法を学びます。フロアプランニングおよび配置の技術を学び、GigaPlace™ソルバーベースの配置を使用しながら、マルチスレッドレイヤー対応のタイミングおよび電力駆動最適化エンジンを使用してタイミングクロージャー戦略を実装し、動的およびリーク電力を削減します。クロスコーナーの変動性を強化し、パフォーマンスを向上させ、電力を削減するために、同時クロックおよびデータパスの最適化エンジンを設定および実行します。

タイミング最適化にトラック認識ルーターを活用し、現代の設計要件に伴う複数の目的を達成する方法を学びます。また、配線違反を診断し修正する方法や、20nm 以下のノードでの設計実装の課題とソリューションを探ります。このコースでは、データベースアクセスコマンド、ワイヤ編集、ECO、および物理検証に関するトピックも扱います。

④ Innovus™ 階層実装と Stylus Common UI トレーニング

このコースでは、最新EDA ベンダ Innovus™ Implementation System ソフトウェアをStylusCommon UI を使用して、階層設計の作成と実装のための技術を学びます。設計をフロアプランニングし、パーティション(階層ブロック)を作成し、配置配線を実行し、設計の最適化を行ってタイミングをクリアする方法を学びます。メモリサイズと実行時間を削減するために、インターフェイスロジックモデル(ILM)を使用する技術を学びます。ブラックボックス、FlexModels、およびSoC アーキテクチャ情報技術を使用して、完全なネットリストが利用できない場合に設計をプロトタイプ化し、統合階層データベース(iHDB)フローを使用してメモリ、実行時間、およびTAT を削減する利点を探ります。

⑤ Tempus™ Signoff タイミング解析と Closure with Stylus Common UI トレーニング

このコースでは、Tempus™ Timing Signoff Solution のタイミングおよび信号整合性解析機能を詳細に探ります。このコースでは、90nm 以下のプロセスノードでの設計に固有のスタティックタイミングと信号整合性の問題を解析します。また、Innovus™ ImplementationSystem with Stylus CUI を使用して、タイミング解析を行い、大規模設計におけるタイミングの問題を特定し、修正する方法を学びます。

使用ツール

- Cadence Genus™ Synthesis

- Cadance Innovus™ Implementation

- Cadance Tempus™ Timing Signoff など

主な対象者

- Linuxのオペレーション経験がある方

- SoC設計の基礎知識を習得している方

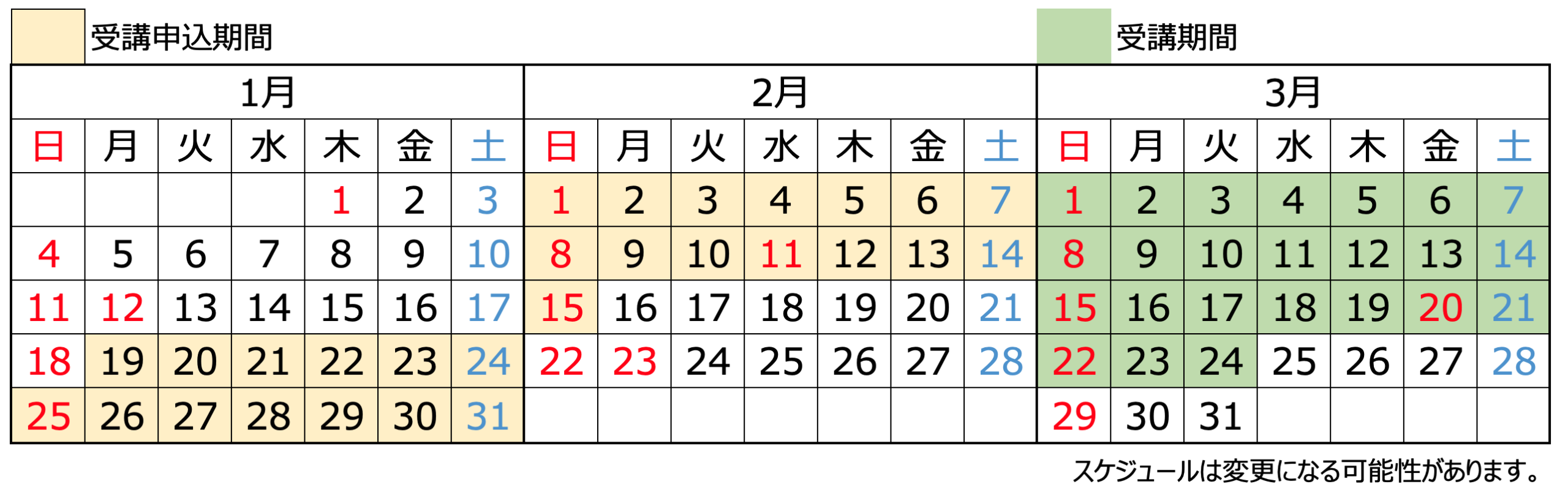

申込手順

開講スケジュール

2026年2月26日~3月25日(計13回、リモート形式) 締め切りました

2026年6月3日〜7月8日(リモート形式)

7月10日〜10月31日(オンデマンド形式)

受講申込期間:4月13日〜5月10日

学習目安時間:75時間

<受講方法について>

リモート(決まった日時に受講)、オンデマンド(期間中都合の良い時間に受講)を、各セクションごとに自由にお選びいただけます。

リモート:原則10:00-17:00 、Zoomでの開催です。リアルタイムで質疑応答も可能ですので、ぜひご検討ください。

オンデマンド:リモート講義の動画を、記載の期間から順次公開します(リモート参加の場合も視聴可)。期間中は何度でも受講が可能です。

※本コースの受講には、事前テストの合格が必要です(既に合格している場合、再受験は不要)。

※日程は変更の可能性があります。

(9) System Design and Verificationコース

コース概要

本コースでは、論理検証にまつわるCadenceのツール群を実践的に用いて、各種スキルを習得することのできる講習を実施します。

最先端の商用EDA Xcelium™ Simulatorを使用してデジタル設計のデバッグとシミュレーションを学び、統合カバレッジ機能を通じて設計の検証範囲を評価します。VerilogやSystemVerilogの言語トレーニングも提供され、デジタルハードウェア設計と検証の基礎から高度な構造までをカバーします。特にSystemVerilogでは、オブジェクト指向設計やアサーション、ランダム化機能を使用した効率的な検証手法に焦点を当てて学習します。

内容

論理検証計ツール群について、その基本機能の講習を実施します。これにより、SoC のRTL 設計、論理検証環境のスキルを習得することができます。

① Xcelium™ シミュレータトレーニング

最新EDA ベンダ Xcelium™シミュレータは、デジタル設計のデバッグとシミュレーションに強力なツールです。この包括的なコースでは、その機能を完全に理解し、設計と検証のプロセスを加速するための高度な機能の使用方法を学びます。講義と実習ラボの組み合わせにより、Xcelium™ のシミュレーションおよびデバッグ機能(波形ビューイング、ソースレベルデッグなど)を探り、Xcelium™ の並列シミュレーション機能を活用して、検証の実行を高速化し、生産性を向上させる方法を学びます。

コース終了時には、最新EDA ベンダ Xcelium™ シミュレータの使用に関する基礎がしっかりと身に付き、複雑な検証課題に自信を持って取り組むためのスキルを習得しています。

② Xcelium™ 統合カバレッジトレーニング

このコースでは、Xcelium™統合カバレッジ機能を探索し、テストベンチが設計をどの程度網羅しているかを測定します。このコースでは、VHDL、Verilog、および混合言語設計のカバレッジを扱います。すべてのカバレッジ機能がすべての言語で利用できるわけではありません。このコースでは、カバレッジのレポートおよび分析にIntegrated Metrics Center を使用し、以下の種類のカバレッジの収集と分析について説明します。

– コードカバレッジ(分岐、式、トグル、状態、アークカバレッジ)

– SystemVerilog カバレッジグループを使用したデータ指向の機能カバレッジ

– SystemVerilog アサーションおよびPSL を使用した制御指向の機能カバレッジ

③ Verilog 言語およびアプリケーショントレーニング

Verilog 言語およびアプリケーションコースでは、Verilog HDL とそのASIC およびプログラマブルロジック設計への応用について包括的に学びます。このコースは、Verilog HDL を使用したデジタルハードウェア設計の基礎を提供し、基本的な概念と構文から合成コーディングスタイルやガイドライン、高度な言語構造および設計検証に至るまでをカバーします。また、ASIC ライブラリ設計の概念にも触れます。

④ SystemVerilog による設計及び検証トレーニング

このコースでは、Verilog ハードウェア記述言語(HDL)に対するSystemVerilog の主な拡張機能について詳しく学び、新機能の利点を議論し、SystemVerilog の構造を使用することで、設計および検証がどのように効率的かつ効果的になるかを示します。

コースは2 つのモジュールに分かれています。設計モジュールでは、RTL 設計および合成の改善点を確認し、検証モジュールでは、オブジェクト指向設計、アサーション、およびランダム化などの検証強化機能を探ります。

使用ツール

- Cadence Xcelium™

- Cadance Verilog HDL など

主な対象者

- Linuxのオペレーション経験がある方

- SoC設計の基礎知識を習得している方

申込手順

開講スケジュール

2026年3月1日~3月24日(オンデマンド形式) 締め切りました

2026年7月14日〜8月28日(リモート形式)

8月21日〜12月31日(オンデマンド形式)

受講申込期間:5月25日〜6月21日

学習目安時間:75時間

<受講方法について>

リモート(決まった日時に受講)、オンデマンド(期間中都合の良い時間に受講)を、各セクションごとに自由にお選びいただけます。

リモート:原則10:00-17:00 、Zoomでの開催です。リアルタイムで質疑応答も可能ですので、ぜひご検討ください。

オンデマンド:リモート講義の動画を、記載の期間から順次公開します(リモート参加の場合も視聴可)。期間中は何度でも受講が可能です。

※本コースの受講には、事前テストの合格が必要です(既に合格している場合、再受験は不要)。

※日程は変更の可能性があります。