〇 概要

上級コースでは、米国サンタクララ・オースティンに拠点を持ち、先端半導体開発をリードしているTenstorrentによるOJTプログラムを実施します。3か月間の事前トレーニングを東京のTenstorrentオフィスで実施後、米国の拠点にて1~1.5年間半導体製品開発の実践的な経験を積むことで、事業全体を俯瞰しながら高度な設計のできる次世代のエンジニア、アーキテクトを育成します。Tenstorrent の一流のエンジニアや関係者と密接に協力しながら、仕様定義、開発項目の決定、エンジニアチームの編成、プロジェクト全体のとりまとめなどを集中的に学び、即戦力となることができます。また、英会話や国際的なコミュニケーション能力、ビジネスセンスを養うことも可能です。

OJTプログラムは、Tenstorrentの開発部門で行われ、RISC-V CPUの設計やAI専用のAIアクセラレータ、Chipletの実装技術などを学ぶことが出来ます。米国本社で現地エンジニア達と共に先端半導体開発を進めることで、設計技術だけでなく、複雑な部門や EDA ベンダを始めとする社外のステークホルダーとの連携など、アーキテクトに欠かせない経験ができます。

Tenstorrent 社について

Tenstorrent社の主な製品について

➢ 目指す設計人材像

開発プロジェクトを牽引するアーキテクト

具体的には、次のような能力をもった人材を目標とします。

- 先端半導体製品を搭載する製品や用途に対する理解

- 半導体製品に求められる仕様を実現し得る内部構造の設計

- 開発する仕様と開発チームの能力との差異の理解、必要な施策の実行

コース修了後、半導体産業で上記のような人材として10年以上活躍する意欲のある方を募集します。

〇 募集要項

➢ 受講対象

本プログラムは、日本国籍を有し、かつ日本に居住している方を受講対象としています。

加えて、上級コースのOJT参加にあたり、Tenstorrentでは次の要件を定めています。

- 必須要件

- J-1ビザが取得できること(渡米時にTenstorrentで支援)

- EE/CSまたは関連分野の学位に相当する学歴を有すること

- Linux、Tcl/Tk、Perl、Python等のプログラミングに精通していること

- 日本語、英語でのコミュニケーション能力を有すること

- あると望ましい要件

- 中・上級エンジニアまたは修士号・博士号取得者であること

- AIアクセラレータ、ASIC設計、FPGAなどの関連分野での実務経験があること

- SystemVerilog等のHDL経験者

- 大規模チップ開発プロジェクトにおけるリーダー経験があること

- EDAツールの高度な使用経験を持つこと

- 技術説明、プレゼンテーション能力を有すること

➢ コース内容

RISC-Vコース、AIアクセレータコースの2つを開講します。RISC-VコースではRISC-V CPUの開発フローを、AIアクセラレータコースではAIハードウェア開発フローを通じたOJTによって、種々のプロセスを身につけます。

いずれのコースも日本で実施する事前トレーニングと、主に米国で実施するメイントレーニングに分かれます。

各コースの詳細は、以下のリンク先よりご確認ください。

事前トレーニング

事前トレーニングでは、2種類の異なる性質の課題に取り組むことで、メインプログラムへの参加に必要な技術的スキル、及びTenstorrentにおけるコミュニケーションや仕事の進め方、ツールの使い方などの総合的な実力を短期間で身につけることを目指します。また、トレーニング全体を通じた評価によって、メインプログラムへの参加可否も判断します。

基本的にIT機器と講師の用意されたTenstorrent東京オフィスでの実施となりますが、遠方に在住の方はオンライン形式でも受講が可能です。(月1~2回程度対面での受講が必須)

メインプログラム

メインプログラムは、ハードウェア設計に関する知識を身につけ、Tenstorrentの開発プロセスを実際に経験し、深く理解することを目指します。また、プロフェッショナルな技術文書の作成や、ビジネスにおけるグローバルなコミュニケーションスキルの向上も重視します。

受講者は開発チームに積極的に参加し、OJTを通じて開発フローにおける種々のプロセスを身につけます。プログラムでは設計、検証、評価等の複数の課題テーマが設定され、実際の業務に即した形で課題を一つずつ経験します。メインプログラムは最短12か月間です。希望する場合、24か月間まで延長することが可能です。

| 事前トレーニング | メインプログラム | |

| 募集/選考期間 | 第2期(締め切りました) 募集:2025年5月7日~8月15日 選考:2025年8月6日~8月22日 第3期(締め切りました) 募集:2025年12月1日~2026年1月30日 選考:2026年2月2日~2026年2月27日 第4期 募集:2026年6月1日~2026年7月31日 選考:2026年8月3日~2026年8月28日 | |

| 定員 | 各期30名 | |

| トレーニング場所 | Tenstorrent日本オフィス(東京都内) | Tenstorrent米国オフィス(Santa Clara/Austin) Tenstorrent日本オフィス(東京都内) |

| トレーニング期間 | 第2期:2025年10月1日~12月26日 第3期:2026年4月1日~6月26日 第4期:2026年10月1日~12月25日 | 第2期:2026年1月5日~(最長2年間) 第3期:2026年7月6日~(最長2年間) 第4期:2027年1月4日~(最長2年間) |

※J-1ビザの都合上、米国の滞在期間は最長18か月となります。

※スケジュールは変更になる可能性があります。

➢ トレーニング期間

上級コースでは、次の順でトレーニングを行います。

1.3か月(国内)

事前トレーニングに該当します。選考過程で必要と判断された技術を補うために、提示される課題に取り組みながら、技術・コミュニケーション力等の総合的な向上を目指します。選考結果によっては、このトレーニングをスキップすることができます。

事前トレーニング全体を通じた評価によって、メインプログラムへの参加可否が判断されます。また、米国OJTへ進まない場合は、国内OJTを継続することもできます。

↓

2.12か月(米国、難しい場合は国内)

1年間米国に滞在し、米国のエンジニアやシニアテクニカルリードと共に2~3の設計工程に関しOJTを行います。

メインプログラムの期間は12か月、18か月、24か月から選択することが可能です。

↓

3.6か月(米国、難しい場合は国内)

希望する場合、引き続き米国に滞在し、米国のエンジニアやシニアテクニカルリードと共にOJTを行います。J-1ビザの都合上、米国の滞在は最長18か月となります。

↓

4.6か月(国内)

Tenstorrent技術チームは合計2年で設計サイクルを完結するため、メインプログラムの期間は最長である2年間を推奨しています。J-1ビザの期限を超えた残り半年は、日本にてリモートで米国エンジニアによる指導や、国内在住のエンジニアからのサポートを受け、設計ノウハウを体得します。

➢ 手続き・費用負担

企業からの参加の場合、必要となる手続きや費用負担は、以下のとおりです。

企業以外からの参加者や、費用について不明な点がある場合は、ADIP運営事務局(以下、「事務局」)までお問い合わせください。

| Tenstorrentとの必要な契約手続き(米国OJT期間中) | 出向契約 |

| 事前トレーニング参加 | 費用負担なし(交通費等は所属する企業で負担) |

| OJT参加(講師費用、EDAツールなどの費用) | 費用負担なし |

| 米国OJT中の給与 | 所属する企業で負担 |

| ・渡航費 ・米国での生活費 (家賃/住居補助、交通費補助、J-1ビザ取得費用、保険費(指定保険)等) | 所属する企業で負担 |

➢ 申込手順

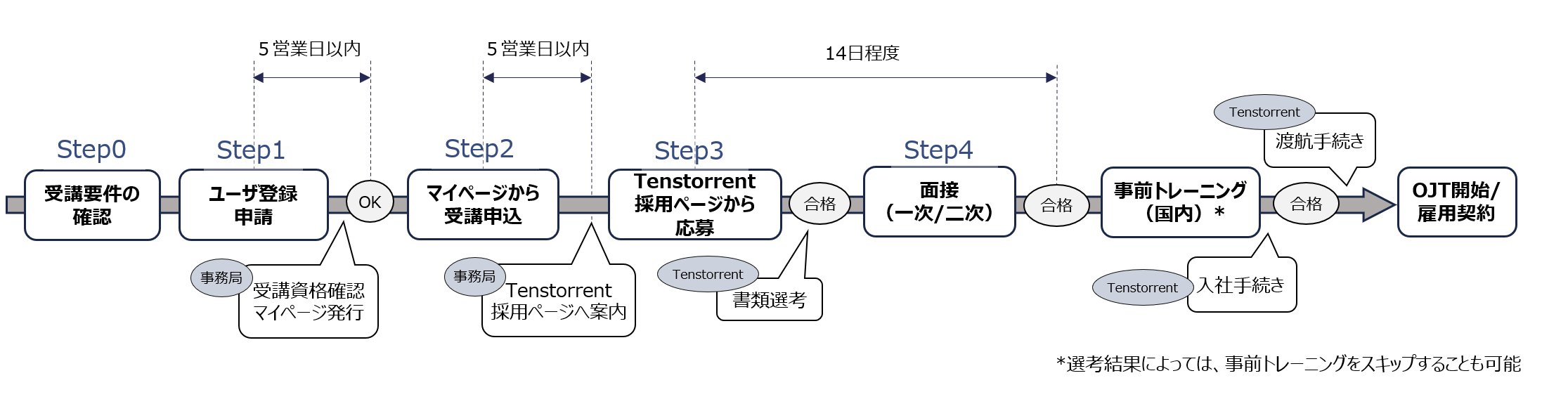

応募からプログラム開始までの流れは、下の図のようになります。次項より申込手順を詳述します。

Step0.

受講要件の確認

上級コースの受講には、本プログラム共通の要件、上級コースのみの要件のどちらも満たす必要があります。

<共通:Step1で判定>

本プログラムは日本の半導体産業において即戦力となるような設計者、アーキテクトを育成し、中長期にわたって日本の産業に資する人材を育成することを目的としています。この趣旨に賛同し長く半導体産業で活躍したいという意欲のある方を、募集します。

本プログラムは半導体設計技術者の育成を目的とし、初級・中級(日本国内で実施)から上級(日本国内・米国で実施)レベルのスキルまで一貫して学べるように構成されています。そのため本プログラムは以下の日本および米国の法令等を遵守する等、 技術流出防止にも配慮します。またカリキュラムの提供に協力いただいている企業等の競争上の地位その他正当な利益を害する恐れの無いように配慮します。

- 外国為替及び外国貿易法(外為法)

- 米国輸出管理規則(EAR)

受講には、以下の要件をいずれも満たしていることも必要です。

- 日本国籍を有すること

- 日本に居住していること

※上級コースに限り、日本に居住していなくても、日本企業所属の方はお申込が可能です。ユーザ登録申請前に事務局までご相談ください。

<上級コースのみ:Step4で判定>

TenstorrentではOJTへの参加にあたり、次の要件を定めています。

- 必須要件

- J-1ビザが取得できること(渡米時にTenstorrentで支援)

- EE/CSまたは関連分野の学位に相当する学歴を有すること

- Linux、Tcl/Tk、Perl、Python等のプログラミングに精通していること

- 日本語、英語でのコミュニケーション能力を有すること

- あると望ましい要件

- 中・上級エンジニアまたは修士号・博士号取得者であること

- AIアクセラレータ、ASIC設計、FPGAなどの関連分野での実務経験があること

- SystemVerilog等のHDL経験者

- 大規模チップ開発プロジェクトにおけるリーダー経験があること

- EDAツールの高度な使用経験を持つこと

- 技術説明、プレゼンテーション能力を有すること

Step1.

ユーザ登録

Step2.

マイページから

受講申込

Step3.

Tenstorrent採用ページ

から応募

事務局より送付されたTenstorrent採用ページから、応募手続きを行ってください。

企業の採用に準じた書類選考を行ったのち、結果及び面接のご案内をTenstorrentよりお送りします。

Step4.

面接

Tenstorrent採用担当による面接を行います。

一次面接では技術、英会話能力、適正等を、二次面接では希望OJTコースでのテクニカルスキル等をチェックします。

選考期間終了後、一次/二次面接の合否結果や及び合格者への事前トレーニングのご案内をTenstorrentよりお送りします。

〇 注意事項

- ユーザ登録申請をする際のメールアドレスは、所属組織が支給する、個人が特定できるメールアドレスに限ります。グループメールや複数の方で共有するメールアドレスでの申請はできません。また、MicrosoftやGoogle等がそれらの従業員以外の一般会員に提供したメールアドレス等での申請もできません。

- マイページの案内は、事務局の審査により本プログラムの受講が認められた方へお送りします。この際の個人情報の取り扱いについては、別途定めるプライバシーポリシーをご参照ください。なお、事務局が受講を認めないと判断した場合でも、不許可の理由は開示いたしませんので、ご了承ください。

〇 応募情報の取り扱いについて

応募に際し申請書等に記載された個人情報のうち、選定や通知、受講等の運営などに必要な情報は、Tenstorrent、及び事務局に共有されます。

またアンケートや特定の個人を識別しない状態に加工した統計資料等に利用することがあります。応募の個人情報は上記目的以外で利用することはありません(法令等により提供を求められた場合を除く)。詳細は、別途定めるプライバシーポリシーをご参照ください。