内容は変更になる可能性があります。

コース概要

オンライン講座で習得した知識を活用し、AIDC が有する最新EDA ツールを使用した演習を行います。設計知識を活用する経験を通じて、短TAT で半導体開発をリードできる人材を目指します。

またチームで演習に取り組むことで、リーダーシップを育みます。

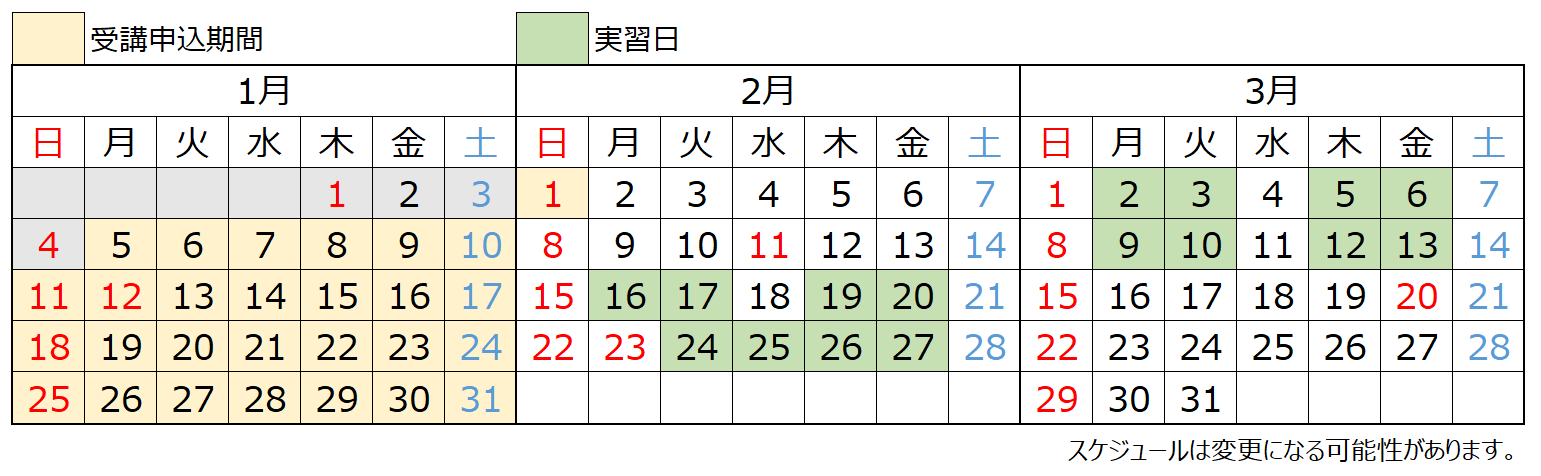

開講スケジュール

2026年2月16日~3月13日(週4回(平日)、全16回(10時30分~17時))

申込期限:2026年2月1日

本コースの受講には、事前テストの合格が必要です(既に合格している場合、再受験は不要)。

受講方法:東京大学構内/オンライン

インターネットを通じて講義や演習に参加でき、ご自宅などから受講が可能です。受講期間中は、日ごとに集合形式とオンライン形式を自由に選択できます。

ただし、初日は環境設定のため、原則として東京大学構内にお越しいただく必要があります。

演習テーマ

各演習は例題回路としてAIDC 所有のAI-One などの設計資産を題材とし、AIDC が有する最新EDA ツールを使った設計作業を体験する。

| 演習テーマ | 詳細 |

|---|---|

| 設計仕様演習 | 要求仕様に基づいて設計仕様書を作成する。この設計仕様書には、ブロック図やタイミング要件といった設計に必要な詳細情報を含める必要がある。設計の初期段階では、例題回路を活用しながら、最適な設計仕様を策定する。作成した設計仕様書は、チーム内でレビューを行い、AIDC のツールを活用して設計に必要なすべての情報が網羅されているか確認する。 |

| 論理設計演習 | 設計仕様書を基に、ハードウェア記述言語を使用して論理設計を進める。この段階では、回路だけでなくテストベンチも記述し、テスト環境を整える。例題回路を論理シミュレータ(Xcelium やVCS)で動作させることで、回路の動作を詳細に検証する。テキストエディタを使用し、シミュレーション結果に基づいて回路の最適化を行う。 |

| 検証項目作成演習 | 設計仕様書に基づいて、回路の検証項目を作成する。検証項目は、回路が仕様通りに動作するかを確認するための基準となる。この項目を基に、例題回路の動作を確認し、商用ツールで効率的に検証を進めることができる。作成した検証項目は、レビューを行い、適切な項目が漏れなく設定されているか確認する。 |

| 論理検証演習 | 論理設計が完了した後は、論理検証を実施する。論理シミュレータを使用して、例題回路の動作を詳細に確認する。検証中に違反が見つかった場合は、その原因を特定し、設計の修正を行う。また、回路図エディタを併用して、回路の動作を視覚的に確認し、問題解決に役立てる。 |

| SDC作成演習 | 要求仕様と回路の構造に基づき、タイミング要件をSDC 形式で記述する。作成したSDC ファイルは、後続のステップで使用され、回路のタイミングを正確に制御する役割を果たす。 例題回路のタイミングを考慮しつつ、商用EDA ツールを用いてフォーマットの確認と、タイミング設定が適切であるか確認するための詳細なレビューを行う。 |

| 論理合成演習 | 論理設計が完了した後、論理合成ツールを用いて設計をゲートレベルに変換する。例題回路を使用し、ツールに対して最適なライブラリと制約を設定し、回路が効率的に動作するゲートネットリストを生成する。出力されたレポートを基に、合成結果の評価を行い、必要に応じて設計を修正する。 |

| ゲートシミュレーション演習 | 論理合成後、ゲートレベルのネットリストを論理シミュレータでシミュレーションし、例題回路の動作を確認する。この段階では、シミュレーションを通じて、回路が意図した通りに動作しているかどうかの確認を行い、問題があれば修正する。ライブラリは遅延付を使用して動的タイミング検証の演習も兼ねる。 |

| Sign-off演習 | BE(バックエンド)演習に進む前に、FE(フロントエンド)で作成した成果物に問題がないかを最終確認する。この段階では、AIDC の商用EDA ツールの結果や、レビューの結果を活用し、最終的な設計が要求仕様を満たしているかを確認する。 |

| フロアプラン演習 | レイアウトツールを使用し、最適なフロアプランを作成する。この段階では、例題回路を活用し、信号の流れや配置を最適化する。設計が物理的に適切にレイアウトされるよう、商用EDA ツールを駆使し、設定やライブラリを正確に取り扱う。演習はフロアプランの面積効率を最大化するために、レイアウトの収縮技術を用いることを主眼に、ツールを使いながら、チップ面積を最小限に抑えるための手法を学び、製造コストやパフォーマンスのバランスを取りながら最適なレイアウトを構築する事を目的とする。 |

| 配置配線演習 | レイアウトツールを用いて自動配置・配線を行う。CTS(クロックツリー合成)を実施し、信号伝播を最適化する。回路の配置や配線の混雑を確認しながら、ツールの操作方法を習得し、最適なレイアウトを試行錯誤する。自動配置・配線後、特定の重要な信号経路やパワーラインに対して手動で微調整を行う演習を追加する。これにより、自動配置では最適化できないクリティカルな配線に対して、最小の遅延やノイズ干渉を避ける手法を習得する。 |

| STA演習 | レイアウトデータを基に、容量抽出ツールを使用して配線容量を抽出し、STA(静的タイミング解析)を実施する。商用ツールを用いて、タイミング制約を満たしているか確認し、必要に応じて設計を修正する。セットアップタイムとホールドタイムを最適化する演習で、商用ツールを使用してセットアップ・ホールドバイオレーションを特定し、各タイミング制約をクリアするための回路設計の見直しを行う。 |

使用ツール

- HDLシミュレータ、回路・波形表示ツール

- RTL分析ツール など

ゴール

- 最新EDAツールを実際に操作し、その使用経験を積む。

- 短TATで半導体開発をリードできるようになる。

- 半導体設計におけるリーダーシップが身につく。